状态机,顾名思义就是用来描述状态的。完善一点就是在同一的时钟下。更准确说是一种verilogHDL编程思想。

例如我们每一个系统都可以分为好几种状态,如:开始,初始化,运行,状态1,状态2,状态3,状态4,结束。

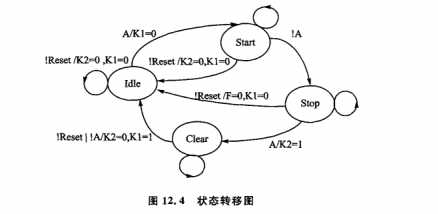

一个系统或者一个物体的行为或者一个器件的状态,我们都可以分成好几种状态,那么就可以画出如下图的状态图,当然不可能所有的状态都是这样,但是大穹小异。这里的输出是用k1,k2来表示的,也就是代表当这种状态的时候,我们系统会实行什么行为。

module fsm(clk,rst,a,k1,k2,state);

input clk,rst,a;

output k1,k2;

output[1:0] state;

reg k1,k2;

reg[1:0] state;

parameter idle=2‘b00,//空闲的

start=2‘b01,

stop=2‘b10,

clear=2‘b11;

always@(posedge clk)

if(!rst)

begin

state<=idle;

k2<=0;

k1<=0;

end

case(state)

idle:

if(a) begin state<=start;k1<=0;end

else begin state<=idle;k2=0;k1=0;end

start:

if(!a) state<=stop;

else state<=stop;

stop:

if(a) begin state<=clear; k2<=1;end

else begin stste<=stop;k2<=0;k1<=0;end

clear:

if(!a) begin state<=idle;k2<=0;k1<=1;end

else begin state<=clear;k2<=0;k1<=1;end

default:

state<=2‘bxx;

endcase

endmodule

parameter idle=4‘b0000,

start=4‘b0100,

stop=4‘b0010,

clear=4‘b0001;

这叫独热码,你懂的。

state<=start; ……………… state<=stoptoclear; …………………… state=idle;

//每一个时钟产生一个状态的改变

always@(posedge clk)

if(!rst)

state<=idle;

else

state<=nextstate;

//产生下一状态的组合逻辑

always@(state or a)

case(state)

idle:

if(a) nextstate=start;

else nextstate=idle;

start:

if(!a) nextstate=stop;

else nextstate=start;

stop:

if(a) nextstate=clear;

else nextstate=stop;

clear:

if(!a) nextstate=idle;

else nextstate=clear;

default:

nextstate=2‘bxx;

endcase

//产生输出k1的组合逻辑

always@(state or rest or a)

if(!rst)

k1=0;

else

if(state==clear&&!a)

k1=1;

else

k1=0;

//产生k2的组合逻辑

always@(state or rst or a)

if(!srt)

k2=0;

else

if(state==stop&&a)

k2=1;

else

k2=0;

不同类型的状态机有不同的优势。

原文:http://www.cnblogs.com/qidaiymm/p/4902530.html