在manaul mode中选择PLL

PLL的输入时钟可以是全局时钟,也可以是普通IO引脚。

1.PLL的输入时钟是全局时钟的情况。

pll_xx pll_xx (

.clkin ( clkin ),

.clkout ( clkout )

);

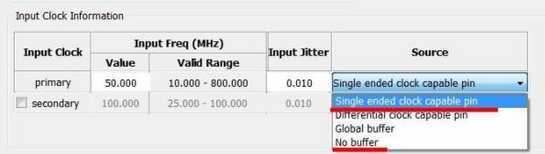

其中clkin为全局时钟输入,在IP核中的设置需要注意SOURCE里的区别,如下所示;

在这种情况下,选择Single ended clock capable pin.

同时,clkout通过ODDR2输出clk_div,这时的clk_div可以接到普通IO引脚,也可以接到全局时钟引脚上。

2.PLL的输入时钟是普通IO

虽然说普通IO不会作为PLL的输入时钟,因为芯片的输入时钟几乎是全局时钟引脚输入。网上说,可以将普通IO时钟通过用BUFG原因输出clk_w,然后clk_w作为PLL的输入时钟,而且IP的输入时钟设置为No buffer,我这样做了,但并没有通过布局布线,弄了半天还是没结果,希望知道的可以留言讨论下。

原文:http://www.cnblogs.com/geekite/p/5042019.html