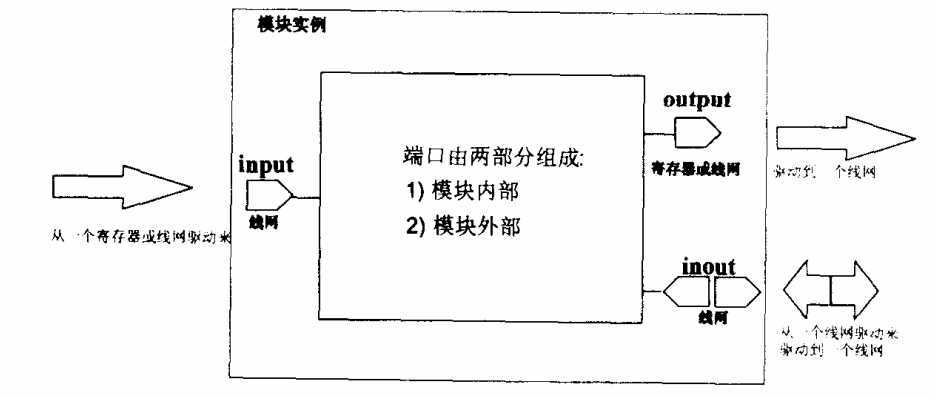

verilog中,一般input默认为wire型,output信号可以是wire型,也可以是reg型(在always或initial中被赋值);

inout是双向信号,一般将其设为tri型,表示其有多个驱动源;

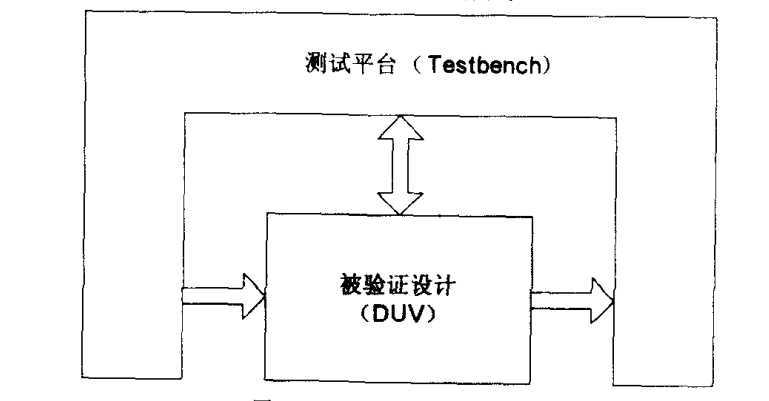

测试脚本编写步骤:1、例化 2、激励 3、结果

在测试脚本中,input—>reg output—>wire

inout—>wire

1、时钟信号产生

方法1:

parameter PERIOD = 20;

initial begin

clk = 0;

forever #(PERIOD/2) clk = ~clk;

end

方法2:

parameter PERIOD = 20;

always begin

#(PERIOD/2) clk = 0;

#(PERIOD/2) clk = 1;

end

2、复位信号产生

方法1:封装成一个task,复位的时候直接调用

initial begin

rst_task(100);//定义复位时间

$stop;

task reset_task;

input [15:0] reset_time;

begin

rst = 0;

#rst_time;

rst = 1;

end

endtask

方法2:

initial begin

rst = 0;

#100;

rst = 1;

#2000;

$stop;

原文:http://www.cnblogs.com/loves6036/p/5070648.html