本人在这只讨论建模好的模块来比较解释现象,如有不周到请大家指正。

软件功能仿真和在硬件上的区别:可以从这个数码管的行扫描和列扫描实例来体会一下,物理时序的影响和改进方法。

数码管的行扫描、列扫描要求同步。即当列扫描扫到一个数码管时、对应该数码管的数字显示必须准备好赋值,依次循环下去。否则显示出现重叠,混乱。

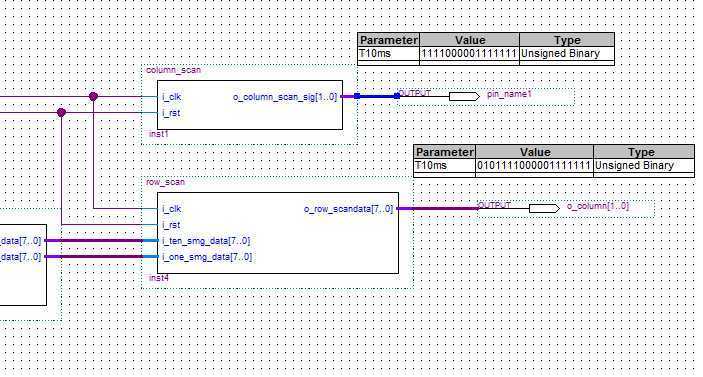

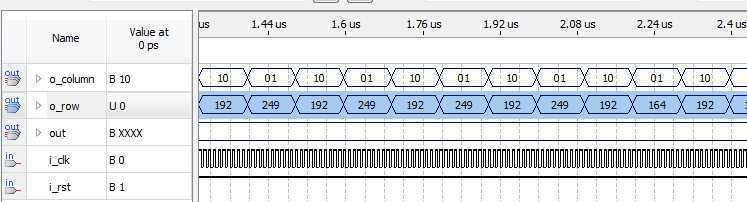

一开始如下建模(行扫描和列扫描都是延时10ms,每隔10ms十位和各位交替工作,同时数码管的段选码给个位和十位赋值)功能仿真:结论很明显,逻辑上是可用的。因为只有两个数码管(十位(10)各位(01))显然十位应该显示一个不变的数字,但是下载到板子上并不是,而是显示混乱重叠,两个管子同时显示一个数字,个位和十位数字一样。这个现象出现的原因是,行列扫描必须是严格同步的,功能仿真没有考虑硬件的物理时序的误差。所以软件仿真是可用的。而在板子上是不可以的。

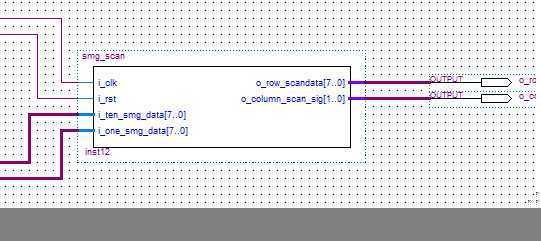

解决方法:把这两个模块的内部联系在一起即可。例如

方法1.把他们内部建成一个相互联系的模块。这样他们的延时,扫描数据同时在目标位同步有效。

row_scan U1

(

.i_clk( i_clk ),

.i_rst( i_rst ),

.i_ten_smg_data( i_ten_smg_data ), // input - from top

.i_one_smg_data( i_one_smg_data ), // input - from top

.o_row_scandata( o_row_scandata ) // output - to top

);

column_scan U2

(

.i_clk( i_clk ),

.i_rst( i_rst ),

.o_column_scan_sig( o_column_scan_sig ) // output - to top

);

顶层文件如下所示;(问题就解决了)数码管就不会乱码

方法2 行列扫描写在一个**.v的文件了。做到同步。和以上的方式异曲同工。

这个实例体会,物理时序和理想时序非常到位。

工匠小建--原创--转载请注明出处--长风破浪会有时,直挂云帆济沧海。

FPGA 物理时序不合理的体现(体现方式:数字钟的行扫描和列扫描)

原文:http://www.cnblogs.com/lsjjob/p/5101765.html