CDC中最重要的问题是metastability问题。

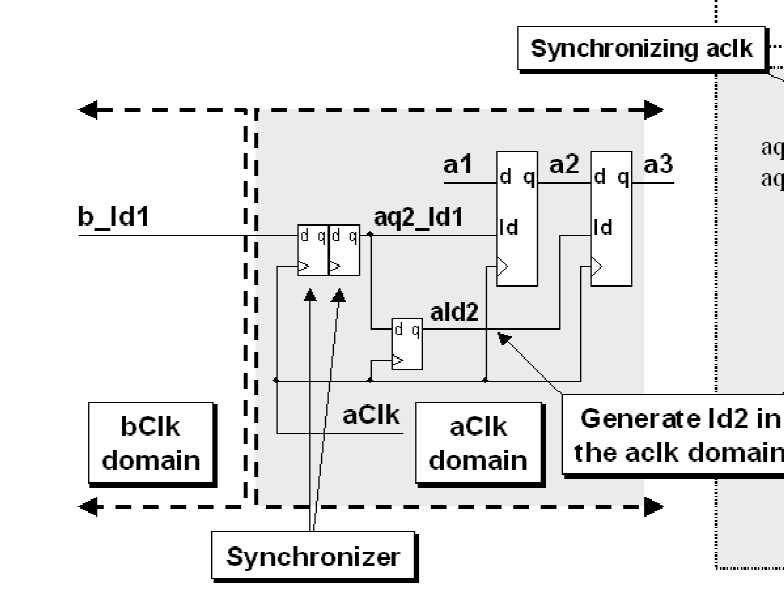

加入Synchronizer来进行异步时钟的同步,两级的Sync,第二级仍然会出现亚稳态的概率由MTBF决定。

MTBF:mean time between fail,数值越大越好,MTBF=1/(Fclk*Fdata*X)。

在频率越高的情况下,MTBF越小,而且clock周期也短,此时可以考虑4级Sync。

在sending clock domain,先将数据用reg打一拍,消除glitch,而且减小了Fdata的频率,这样做CDC时,效果会更好。

从一个slow clock domain到一个fast clock domain,通常不会出现问题。

从一个fast clock domain到一个slow clock domain中时,可能会出现signal没有被采样到的情况。

在这样的情况下,可以:

1)open-loop;

如果要确保信号能被下一级未经sync采样到,信号必须stay 至少3个destination clock。

如果下级有做sync处理,信号stay1.5个destination clock即可。

2)close-loop;

由于req/ack的两级同步处理,会导致通信效率不高。

多比特(Multi-bit)的CDC处理:

1)尽量减少到1bit来进行处理;

2)使用不同的load signal来进行传输;

3)使用gray code;

4)FIFO;

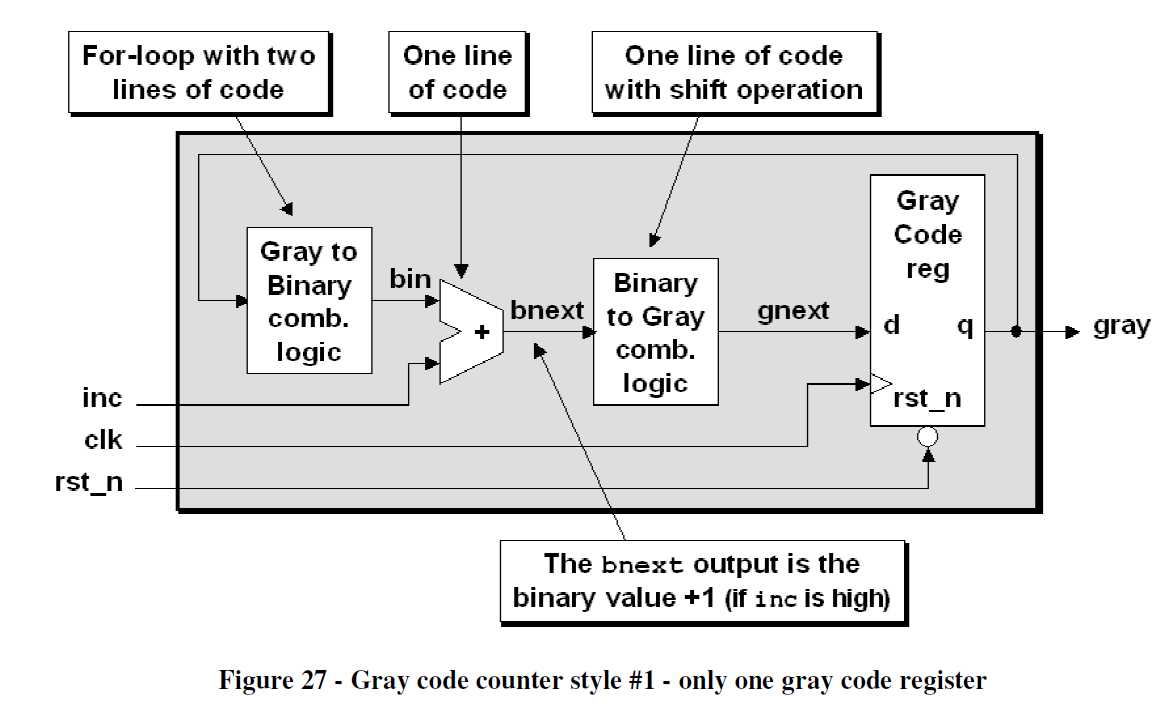

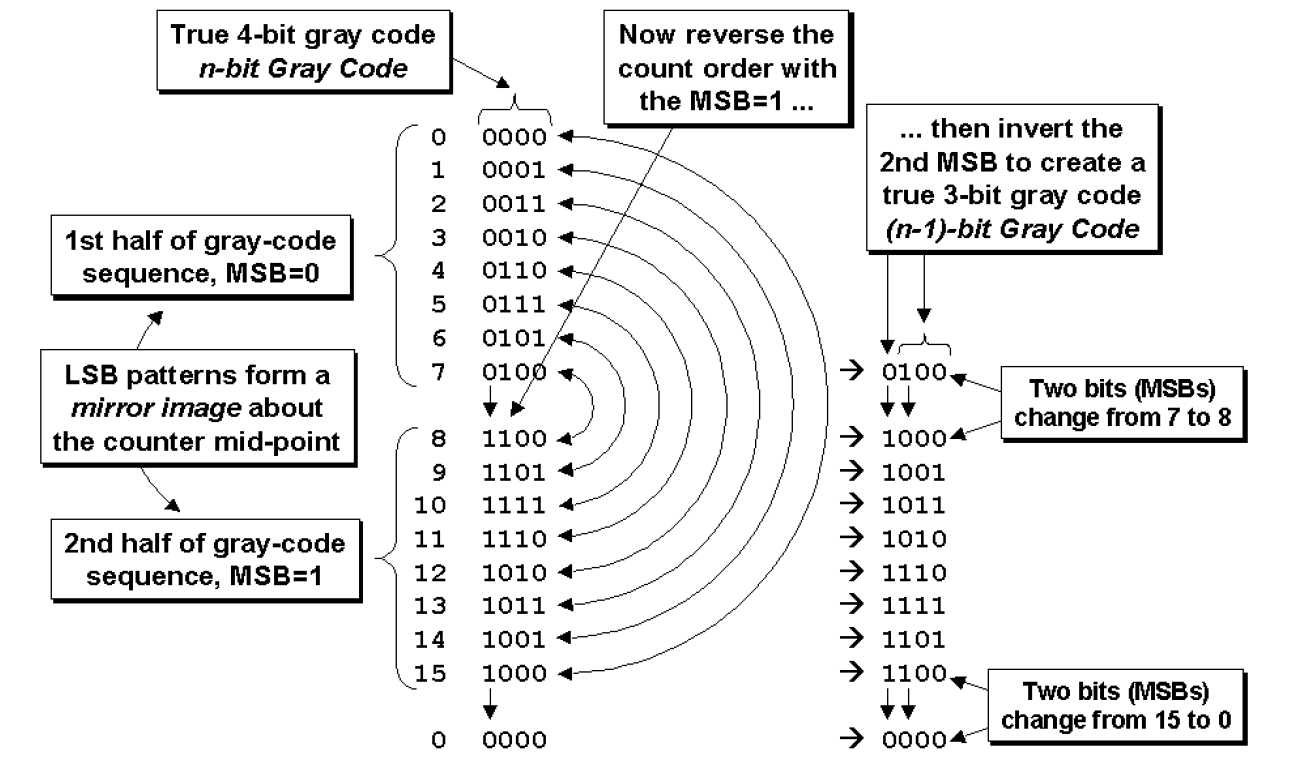

Binary counter会出现多位变化,所以多使用gray counter。

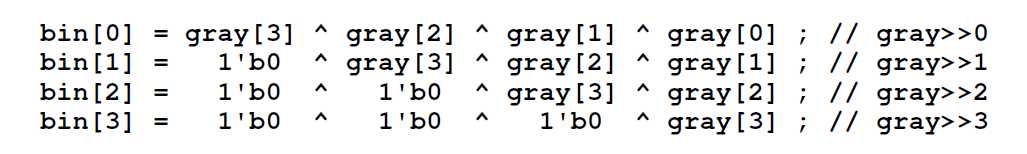

Gray-binary的conversion

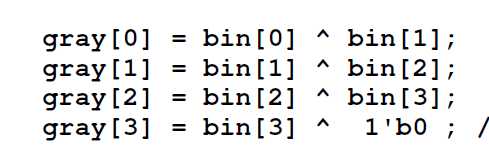

binary-gray的conversion

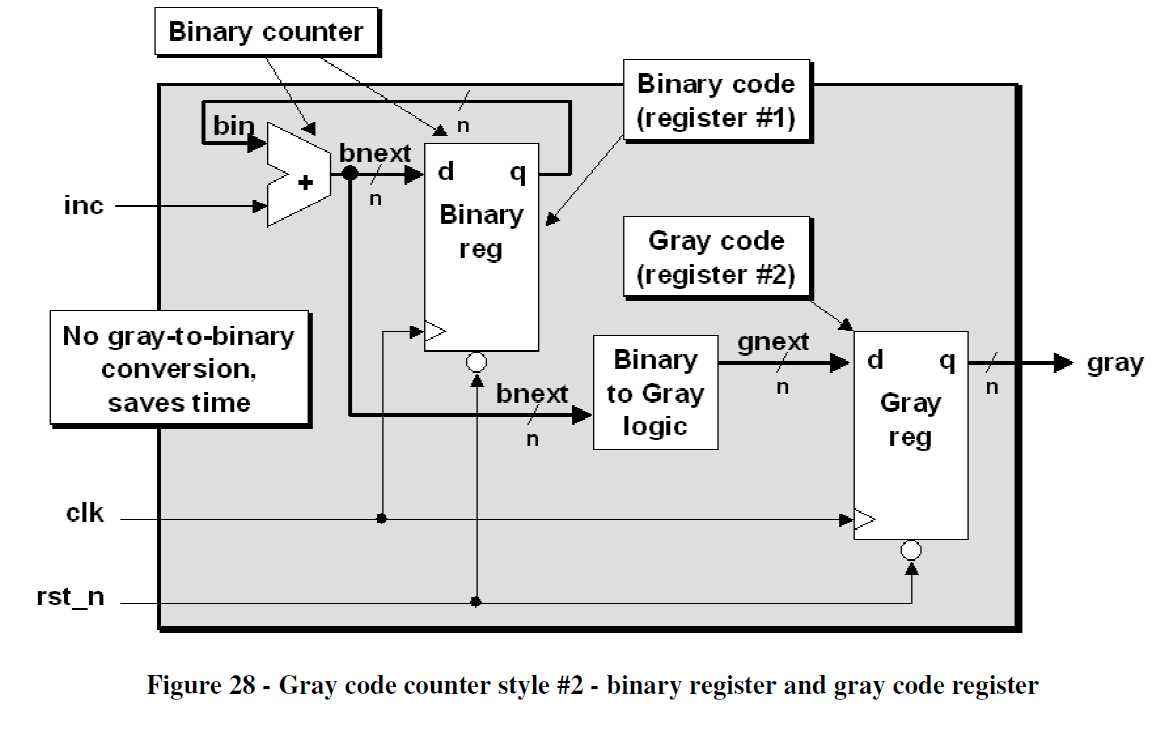

异步FIFO中的两种结构:

1)只含一个寄存器

2)含有两个寄存器,但是少一个conversion的逻辑

在异步fifo的结构中,两个clock domain通信gray编码的wptr和rptr,来产生empty和full的信号。

gray到binary的转换主要是为了进行自加运算。

在empty和full信号的产生过程中,需要增加一比特来进行判断。如4bit的ptr,只有下三位用于计数,

最高位用于循环,在wptr[2:0]=rptr[2:0]时,根据wptr[4]和rptr[4]的值来判断full和empty。

但是当fifo中使用gray code来判断full/empty时,就无法用这个方法。

所以实际中,此处会进行gray code的变形:

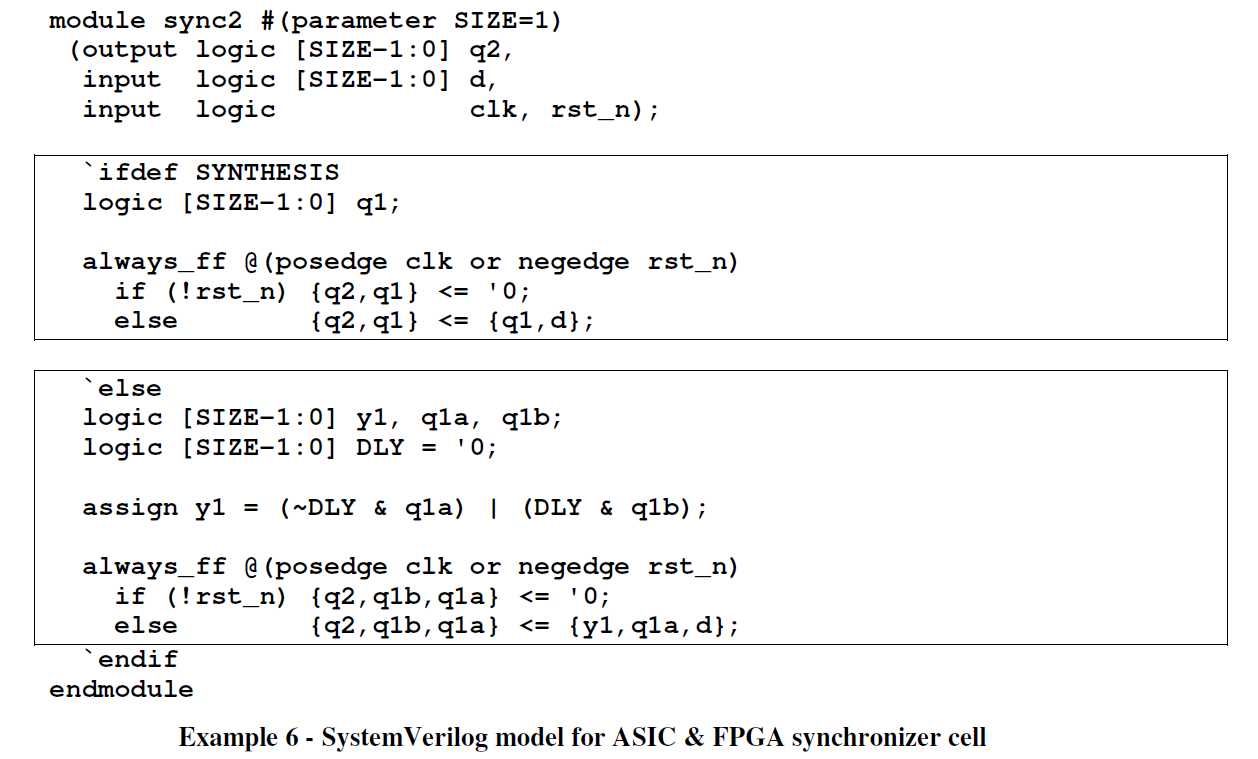

由于sync的存在,第一级的sync很可能造成setup/hold的violation,所以此处在simulation的过程中

应该关掉check。

几种方法:

1)关掉timing check。

2)将lib中的FF的setup和hold time的值都改为0。

3)copy modify FF,指定sync单元使用修改过的FF。

4)手动或脚本修改sdf中指定路径的setup和hold的值。

5)使用多个sdf文件,在一个文件中修改,在分别读入两个sdf文件,用后一个覆盖前一个。

6)使用verdor提供的支持synchronizer的cell,0-setup,0-hold。

simulation model的建立

其中synthesis控制DC综合的流程。

原文:http://www.cnblogs.com/-9-8/p/5475159.html