verilog设计进阶

时间:2014年5月6日星期二

主要收获:

1. 自己动手写了第一个verilog程序。

题目:

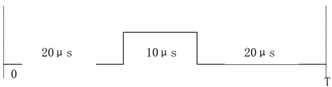

利用10M的时钟,设计一个单周期形状如下的周期波形。

思考:

最开始的想法是:定义两个计数器进行计数,两个使能标志位分别控制这两个变量。但是这样逻辑又太复杂,网上搜了搜,还是定义一个计数器比较好。

verilog程序:

module fdivision(clk, rst, clk_out);

input clk;

input rst;

output clk_out;

reg[5:0] count;

reg rclk_out;

assign clk_out = rclk_out;

always@(posedge clk or negedge rst) begin

if(!rst) begin

count<=0;rclk_out<=0;

end

else if(count==30)

count<=0;

else count<=count+1;

end

always@(posedge clk) begin

if(count<=9) rclk_out<=1;

else rclk_out<=0;

end

endmodule

测试文件:

`timescale 1ns/1ns

module fdivision_test;

reg clk, rst;

wire clk_out;

always #2 clk=~clk;

initial begin

clk=0;rst=1;

#20 rst=0;

#20 rst=1;

#500 $stop;

end

fdivision u1(clk, rst, clk_out);

endmodule

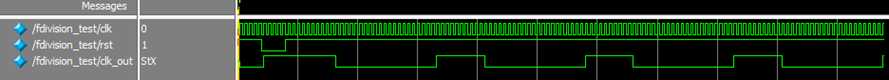

仿真波形图:

原文:http://www.cnblogs.com/510602159-Yano/p/3726021.html