一、STM32外部中断

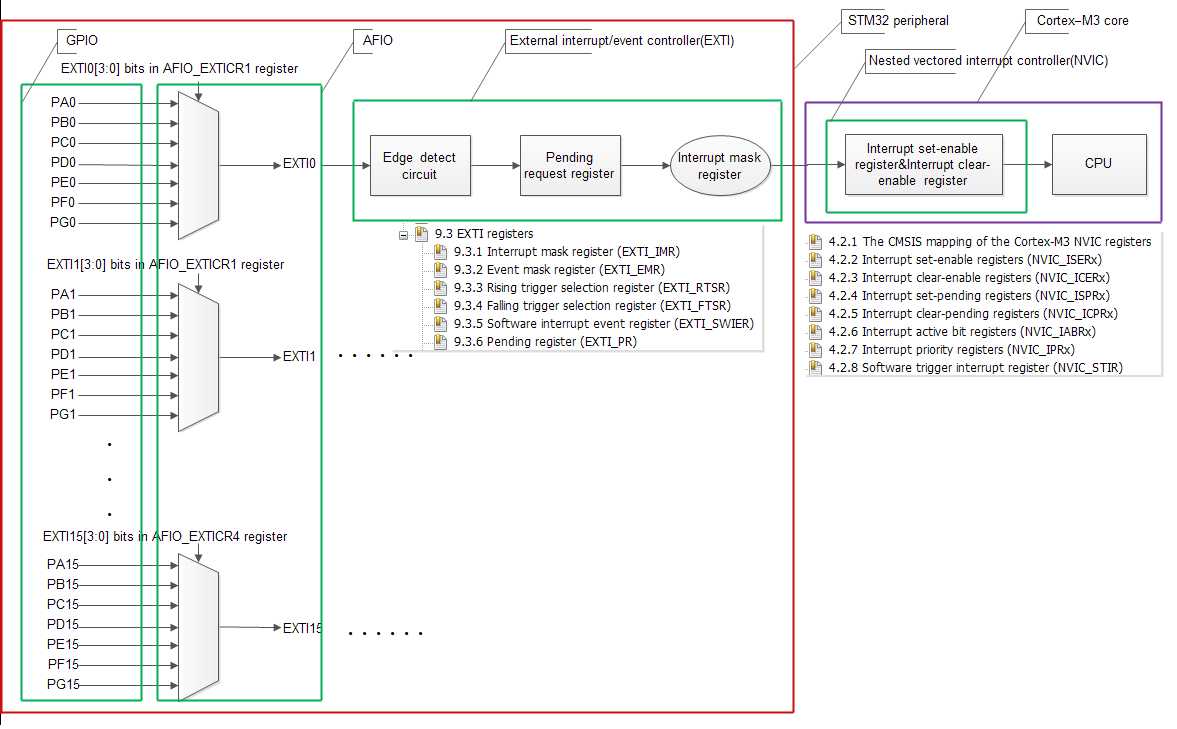

1、STM32外部中断结构图

如上图所示:

主要包括四个环节,GPIO、AFIO、EXTI、NVIC。

2、STM32外部中断软件配置步骤

① 配置NVIC控制器

② 使能GPIO和AFIO时钟

③ 配置GPIO (复用功能的输入输出配置)

④ 配置AFIO (选定要配置为EXTI的I/O口线)

⑤ EXTI控制器的配置

配置寄存器就好像是我们在更改STM32的硬件电路,让它们处于一种新的工作状态--外部中断模式。

二、STM32外部中断软件配置细节

以PA0引脚的外部中断为例进行介绍:

1、配置NVIC控制器

PA0引脚对应的外部中断线是EXTI_Line0,而EXTI_Line0对应的中断源是EXTI0_IRQn。

调用NVIC_Init函数设置中断源EXTI0_IRQn的抢占优先级和响应优先级,并且使能中断。

NVIC_InitStructure.NVIC_IRQChannel = EXTI0_IRQn; NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0; NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE; NVIC_Init(&NVIC_InitStructure);

NVIC_IRQChannel

定义配置的对象,是哪一个中断源,它不能使用 “EXTI0_IRQn|EXTI0_IRQn”方式调用一次NVIC_Init函数配置多个中断源

2、使能GPIO和AFIO时钟

GPIO用作EXTI外部中断或使用重映射功能的时候,不仅需要开启外设时钟RCC_APB2Periph_GPIOA,还需要开启AFIO时钟RCC_APB2Periph_AFIO。

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_AFIO,ENABLE);

3、配置GPIO(复用功能的输入输出配置)

配置PA0为上拉输入。

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0; GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IPU; // 上拉输入 GPIO_Init(GPIOA, &GPIO_InitStructure);

4、配置AFIO(选定要配置为EXTI的I/O口线)

PA0引脚对应的外部中断线是EXTI_Line0,但是PB0~PG0对应的也都是这个外部中断线。所以,需要通过多路选择器确定到底是哪一个引脚映射到EXTI_Line0。

GPIO_EXTILineConfig(GPIO_PortSourceGPIOA, GPIO_PinSource0);

5、EXTI控制器的配置

配置外部中断线EXTI_Line0的工作模式,为中断模式,下降沿触发中断,并且使能外部中断线EXTI_Line0。

EXTI_InitStructure.EXTI_Line = EXTI_Line0; EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt; EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Falling; //下降沿中断 EXTI_InitStructure.EXTI_LineCmd = ENABLE; EXTI_Init(&EXTI_InitStructure);

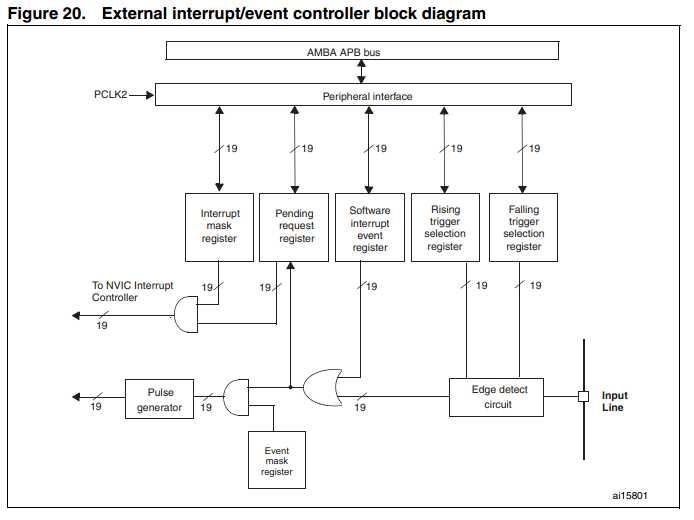

EXTI控制器结构图

三、中断配置过程以及STM中断结构解惑

1、为什么NVIC有使能中断,EXTI控制器还有一个使能控制呢?

NVIC控制器是在ARM公司设计的Cortex-M3内核中,EXTI控制器是ST公司自己设计的外设。

在NVIC控制器中,有“Interrupt set-enable register&Interrupt clear-enable register”,它们来控制是否使能中断源EXTI0_IRQn。

而EXTI控制器中,有“Interrupt mask register”来控制中断线EXTI_Line0的中断标志位是否传送给NVIC控制器。

2、为什么NVIC控制器使能中断源的寄存器要两种?

中断的使能与除能分别使用各自的寄存器来控制——这与传统的,使用单一比特的两个状态来表达使能与除能是不同的。CM3 中可以有 240 对使能位/除能位(SETENA 位/CLRENA 位),每个中断拥有一对。这 240 个对子分布在 8 对32位寄存器中(最后一对没有用完)。欲使能一个中断,我们需要写1 到对应SETENA的位中;欲除能一个中断,你需要写 1 到对应的CLRENA位中。如果往它们中写0,则不会有任何效果。

写零无效是个很关键的设计理念:通过这种方式,使能/除能中断时只需把“当事位”写成 1,其它的位可以全部为零。再也不用像以前那样,害怕有些位被写入0 而破坏其对应的中断设置(反正现在写 0 没有效果了),从而实现每个中断都可以自顾地设置,而互不侵犯——只需单一的写指令,不再需要读-改-写三步曲。(摘自《CM3权威指南》)

3、在清除中断标志位的时候,为什么只需要清除EXTI的中断标志位就行,而不需要清除NVIC的悬起寄存器SETPEND?

有些程序员在中断服务程序结束的位置清除中断源的时候,还调用了NVIC_ClearPendingIRQ()函数清除中断源的悬起标志位,其实是不需要的。

如果中断发生时,正在处理同级或高优先级异常,或者被掩蔽,则中断不能立即得到响应。此时中断被悬起。中断的悬起状态可以通过“中断设置悬起寄存器(SETPEND) ”和“中断悬起清除寄存器(CLRPEND) ”来读取,还可以写它们来手工悬起中断。(这段文字摘自《CM3权威指南》)

由此我们可以得出结论:如果中断服务程序得到执行(中断得到响应),此时中断就不会被悬起。所以我们的中断服务程序不需要清除“悬起标志位”。

有人可能还会这么想:倘若一个中断服务程序因为处理器正在执行同级中断服务程序而不能被执行,中断被悬起,那么当轮到这个中断得到响应后,这个中断服务程序需要清楚“悬起标志位”吗?

我认为还是不需要,因为中断标志位的悬起和解悬,硬件都是可以自动控制的。也就是说,当悬起的中断被响应的时候,“悬起标志位”自动被硬件予以清除,不必手动清除。

参考资料:《STM32 库开发实战指南》

《CM3权威指南》

《STM32F10X芯片手册》

《STM32F10xxx Cortex-M3 programming manual.pdf》

原文:http://www.cnblogs.com/amanlikethis/p/3726247.html