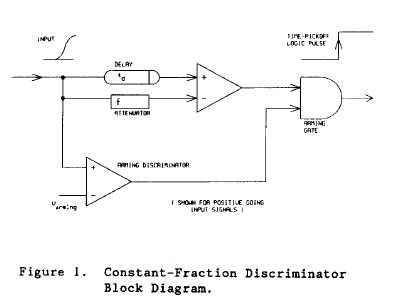

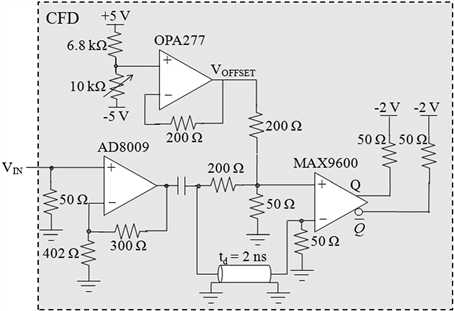

恒比鉴相器CFD是一种新型的能够在高频(100MHz以上)使用的一种鉴相器,与传统的鉴相器的区别在于,CFD的输出与输入的相位差不受输入的大小的改变而变化。实际上都有200~400ps的time walk(时间游动效应),此方式在时间测量领域有着广阔的应用。该方法第一次出现在1967年,由Gedck和MC Donald第一次提出。具体电路如下:

信号被分成两路,一路通过定值比较器去除噪声干扰,另一路分成两路后,一路进过延时,一路衰减(保证相位差和幅值不同),进入过零比较器,两路比较器的输出进入触发器,得到最终输出。一般而言其偏差在400ps左右,在前置加入ACG电路,可以降低整个CFD电路的动态范围,可以将误差减小至200多ps,这样对于高能粒子或是光的时间测量的误差,可以减小到1s左右。一般是对于单一脉冲的时间测量,从而得到回波信号。

基本原理的推到不再赘述,可以假设输入是高斯钟形信号,在延时,衰减之后便可以得到最后的时间表达式,发现其输出值与输入值的大小变化无关,只与过零比较的时间点有关,动态范围很高(我这里的动态范围在80左右)。

实际在操作中,会发现由于时间的抖动的情况,不同幅值下,CFD的输出在时间上依然有微小的位移,这个位移的大小与上升的时间有关,在添加ACG电路之后,其位移会减小,但是整个电路的时间上的反应时间则会大大的加强。整个输入与输出的时间偏移量可能超过30ns,然而在无ACG电路时则是5ns以内,这个是要考虑好的一个重要的因素。

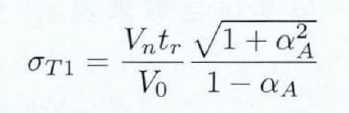

此外关于整个CFD的时间上的鉴别标准差的考量,标准差的大小与信噪比成反比,与上升沿时间成正比。公式如下,其中阿尔法为衰减系数。

CFD由于是超高速的电路,所以在比较器的选择上应该采用ECL(射级耦合逻辑电平)或PECL(正射级耦合逻辑电平Positive Emitter Coupled Logic)。ECL电平 ECL(EmitterCoupled Logic)即射极耦合逻辑,是带有射随输出结构的典型输入输出接口电路,ECL电路的最大特点是其基本门电路工作在非饱和状态,因此ECL又称为非饱和性逻辑。也正因为如此,ECL电路的最大优点是具有相当高的速度。这种电路的平均延迟时间可达几个ns数量级甚至更少。传统的ECL以VCC为零电压,VEE为-5.2 V电源,VOH=VCC-0.9 V=-0.9 V,VOL=VCC-1.7 V=-1.7 V,所以ECL电路的逻辑摆幅较小(仅约0.8 V)。当电路从一种状态过渡到另一种状态时,对寄生电容的充放电时间将减少,这也是ECL电路具有高开关速度的重要原因。另外,ECL电路是由一个差分对管和一对射随器组成的,所以输入阻抗大,输出阻抗小,驱动能力强,信号检测能力高,差分输出,抗共模干扰能力强;但是由于单元门的开关管对是轮流导通的,对整个电路来讲没有“截止”状态,所以电路的功耗较大。需要做好良好的电路散射工作。

如果是从事一般的电子工程师,很少会接触到时间抖动的误差问题。

在《PET系统基础之时间信息概述》一文中提到了arrival time的晃动是导致测量误差重要因素。那么又是什么导致的时间晃动呢,主要有以下几个因素:

1、 探测器的固有晃动。

2、 噪声引起时检点路输出的时间晃动。

3、?幅度时间游动效应。

4、?上升时间游动效应。

以上几种因素在不同条件喜爱对晃动所起的影响是不同的,因为要具体加以分析,分清主次。应着重分析幅度和上升时间游动效应产生的时间晃动及其解决办法。另外,上述列出的因素,主要讨论的是信号调理阶段,也即模拟信号处理。在后端时间量化的时候,也会存在所谓的量化误差(比如TDC误差、时钟Skew和jitter等),这是另外一个概念,这里论述的是时间定时的基础,如果基础不精确也就谈不上后续TDC的测量精度了。

首先我们来看探测器固有晃动,这是因为不同探测器元件的电流信号输出的时间晃动不一样,产生原因也不相同,大致因为载流子在探测器内运动途径不同造成。至于PET系统,其探测器是PMT,由于伽玛光子击中的位置不同使得光传输到PMT的时间不同,这样其输出信号的时间发生差异,而击中的位置往往是随机的,因为信号输出的时间产生晃动。对于这个因素,目前信号调理电路还没有好的办法应对,只能是在挑选PMT的时候下功夫,另外通过多次试验可以在后端对PMT传输时间进行Time Correction,这个Correction的参数通过大量实验获取,并能随时进行更新,所以现在也基本能保证对探测器固有晃动进行很好的补偿。

第二个因素是噪声,噪声叠加在信号上会引起时检电路输出的时间晃动,这个需要通过提高调理电路设计来进行处理,这里不展开。

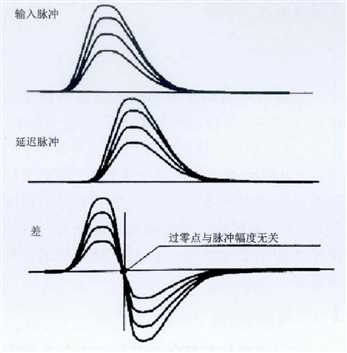

第三个因素是幅度时间游动效应,探测器输出信号的随机变化造成了时间上晃动,称为幅度时间游动效应。不同幅度经过时检电路之后在输出时间上产生差异,如图2所示。

图2:幅度时间游动效应

最后一个因素就是上升时间游动效应,PMT的输出信号上升存在随机变化,这就带来了时检电路的输出信号在时间上晃动,这称为上升时间游动效应。不同的上升时间的信号经过时间检测电路之后会产生在输出信号时间上的差异,如图3所示。

图3:上升时间游动效应

通过图2和图3,那么我可以假设同一个信号通过不同的PMT那么得到不同的幅度以及不同的上升时间,按图示,我们必然会得到不同的定时,这种定时误差必须通过相应的时间检测电路进行避免。

时间晃动大小的度量

具体的理论推导公式以及实验不是笔者的重点,相关的参考文件上可以找到详细的内容。这里借用参考材料上推论时间晃动大小度量时做的实验模型来说明另外一个问题。如图3所示,这是参考资料上实验示意框图。

图4:时间晃动实验测量

这里笔者需要强调的是,图4所示的实验,在PET系统设计中也用得到。一个PET设计完成之后,需要做大量如图4所示的实验,由于PET系统中探测器采用PMT,一个系统有好几百个PMT,尽管PMT采用同一厂家同一批次,但是PMT之间的差异总是存在的,应用图4所示的实验需要获取每一个PMT的光子传输时间信息,有了这些数据才能在后端数字处理的时候进行Time Correction补偿。

由于从事的该项目尚未结题,故更多详细的参数以及完整的电路设计还不能公布。若我有幸能够被读者读到该文,甚至说读者对此方面比较感兴趣,则可以在IEEE explore等其它网站,搜索相关的外文论文,进行阅读,如果还有问题,欢迎私信讨论。

这是该鲤鱼王的第一篇博客,也是一个比较冷门和乏味的领域,从此开始便开始了冒险之旅。

浅谈CFD(constant fraction discriminator恒比鉴相器)

原文:http://www.cnblogs.com/decentman/p/6421054.html