Xilinx FPGA开发环境vivado使用流程

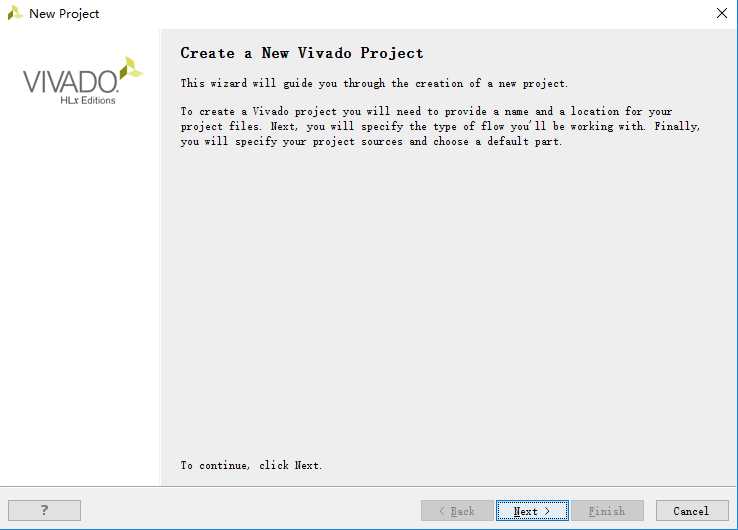

1.启动vivado 2016.1

2.选择Create New Project

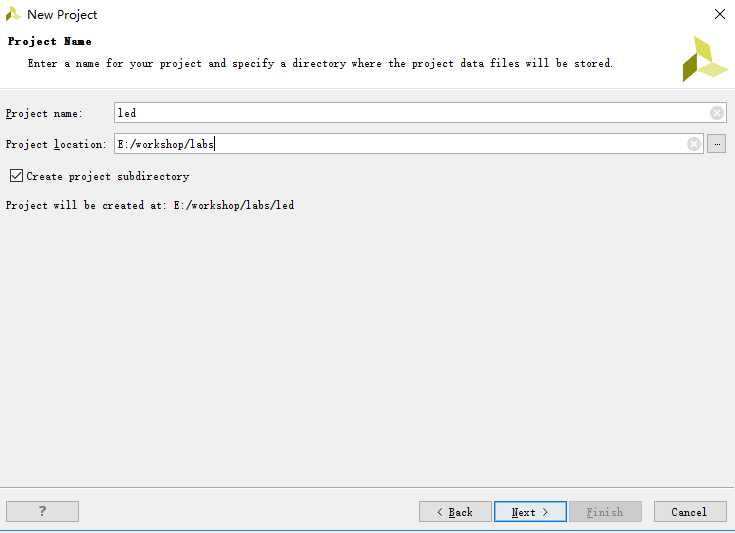

3.指定工程名字和工程存放目录

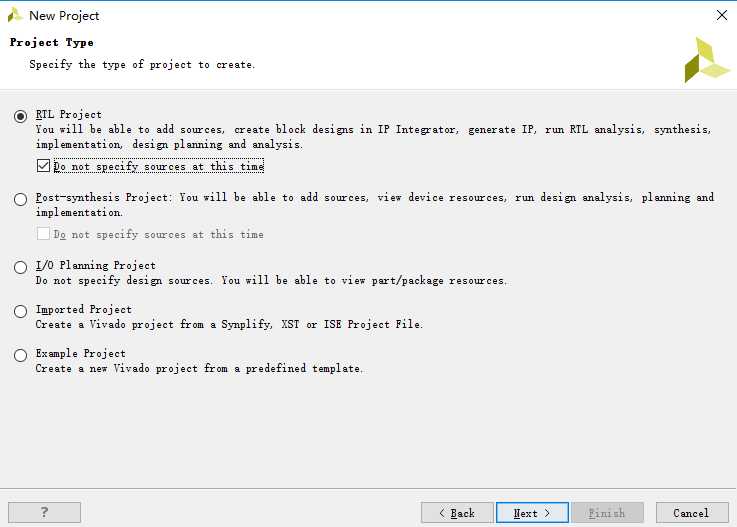

4.选择RTL Project

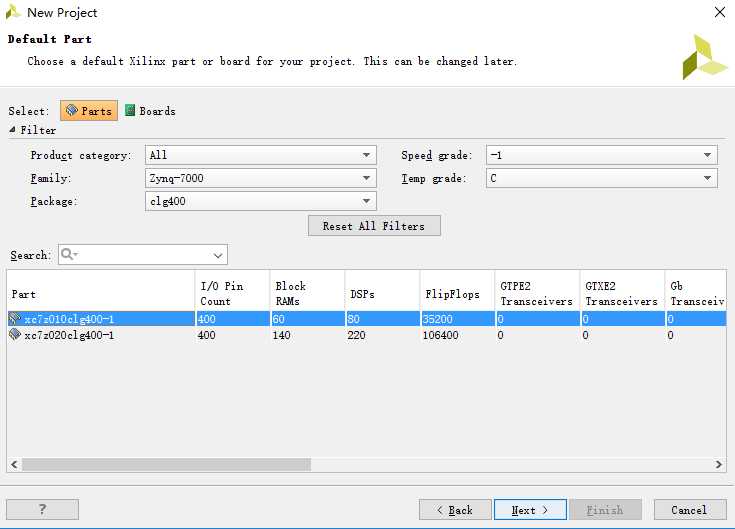

5.选择FPGA设备

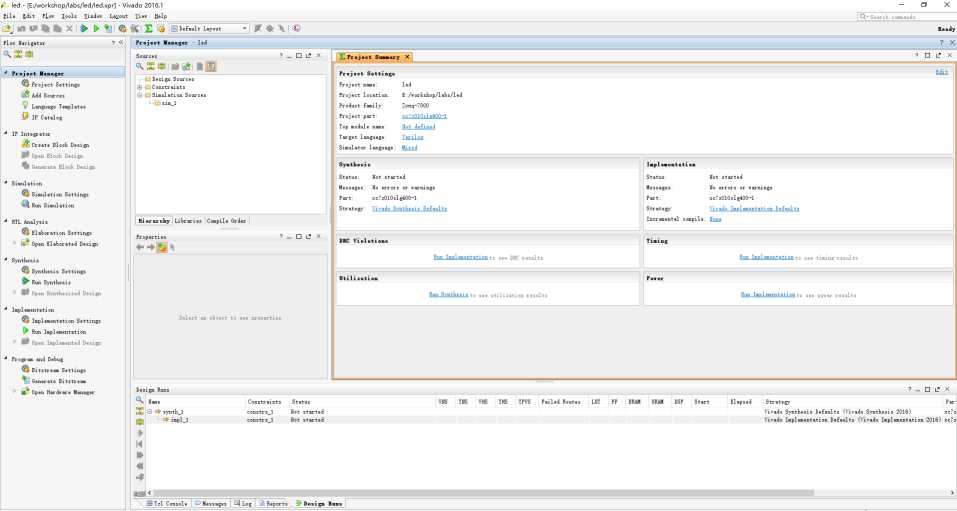

6.工程创建完成后

7.开始编写verilog代码

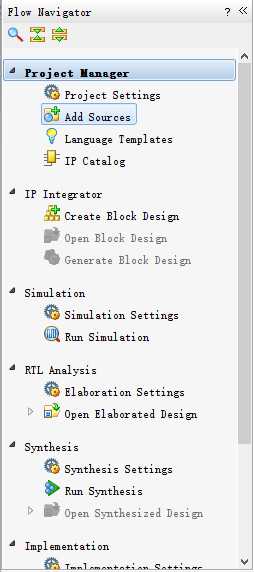

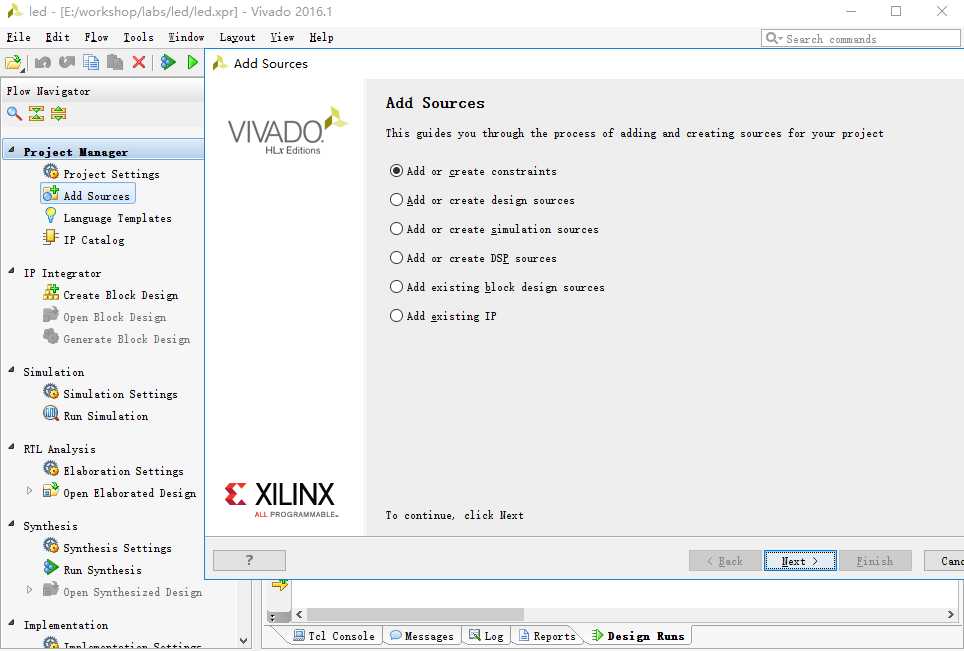

第一步:点击Add Sources按钮

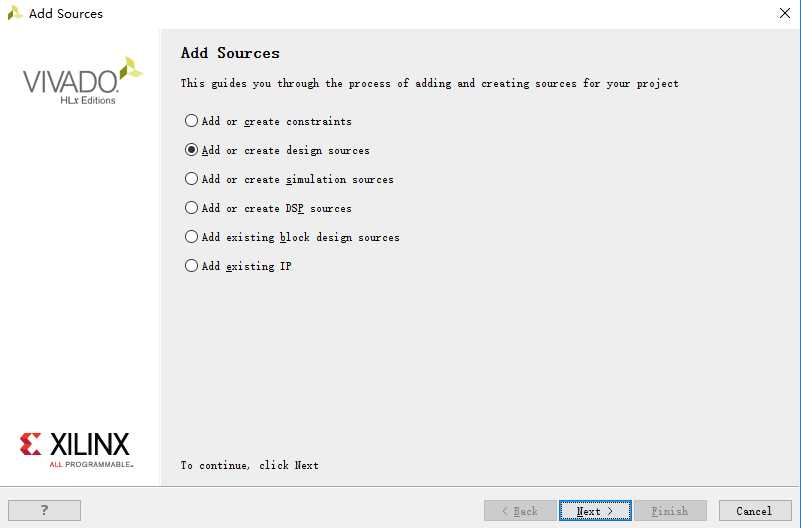

第二步:选择add or create design sources按钮,即添加设计文件

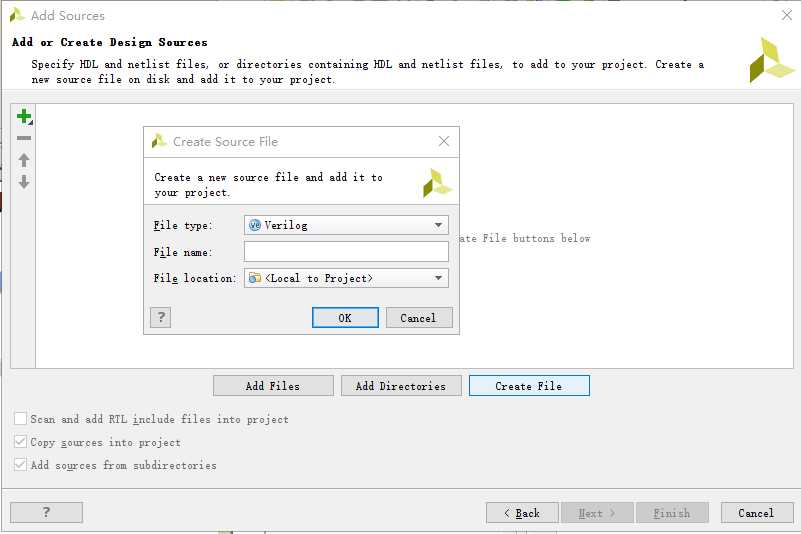

第三步:选择create file

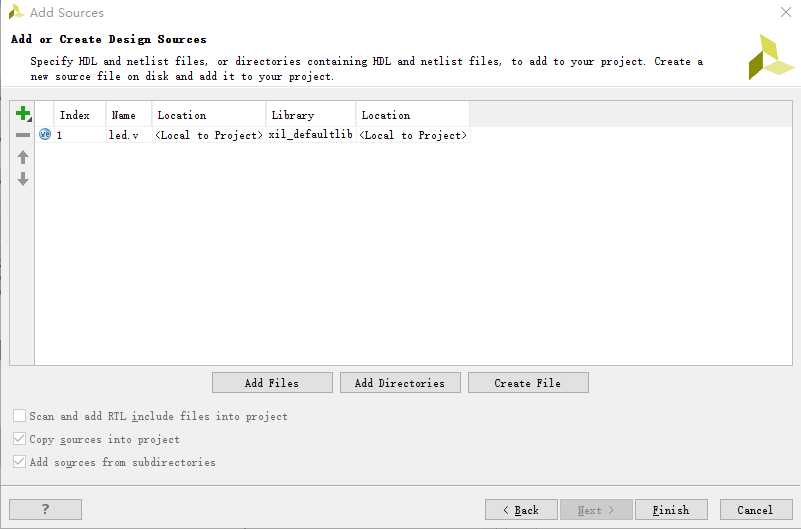

文件新建完成后:

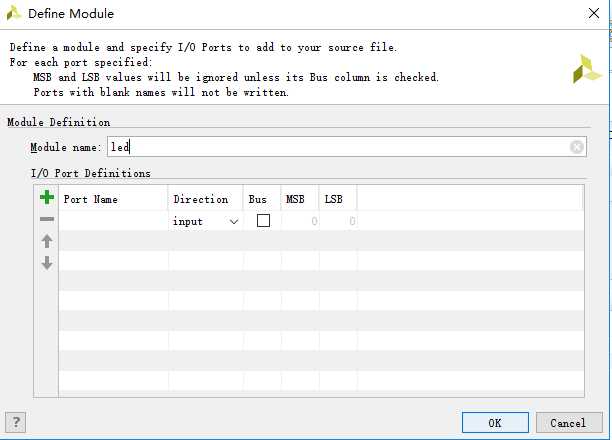

此时可以定义I/O端口,我们选择自己在程序中编写。

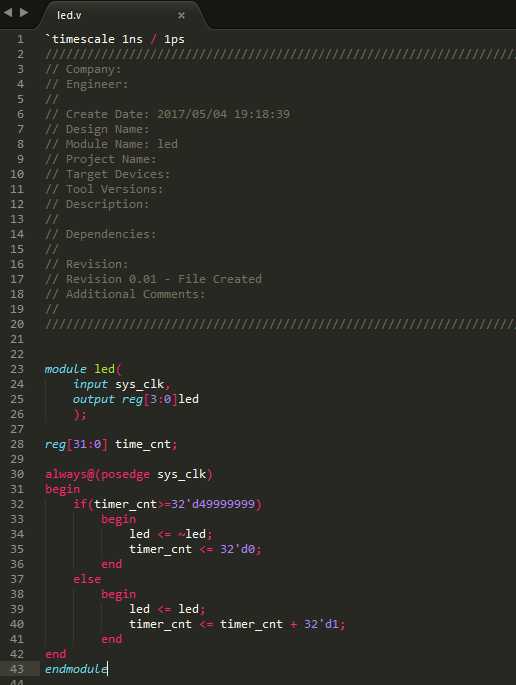

第三步:在编辑器中编写verilog程序

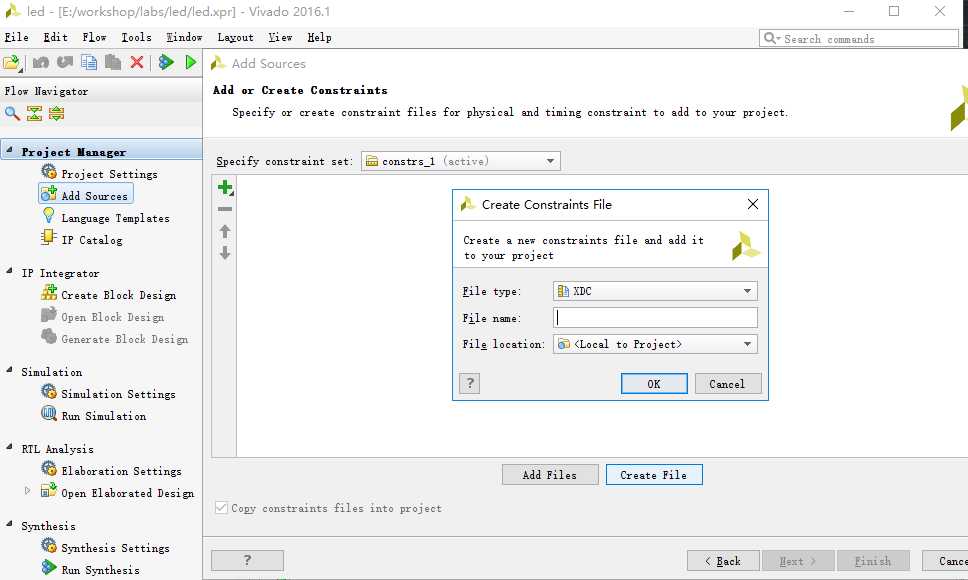

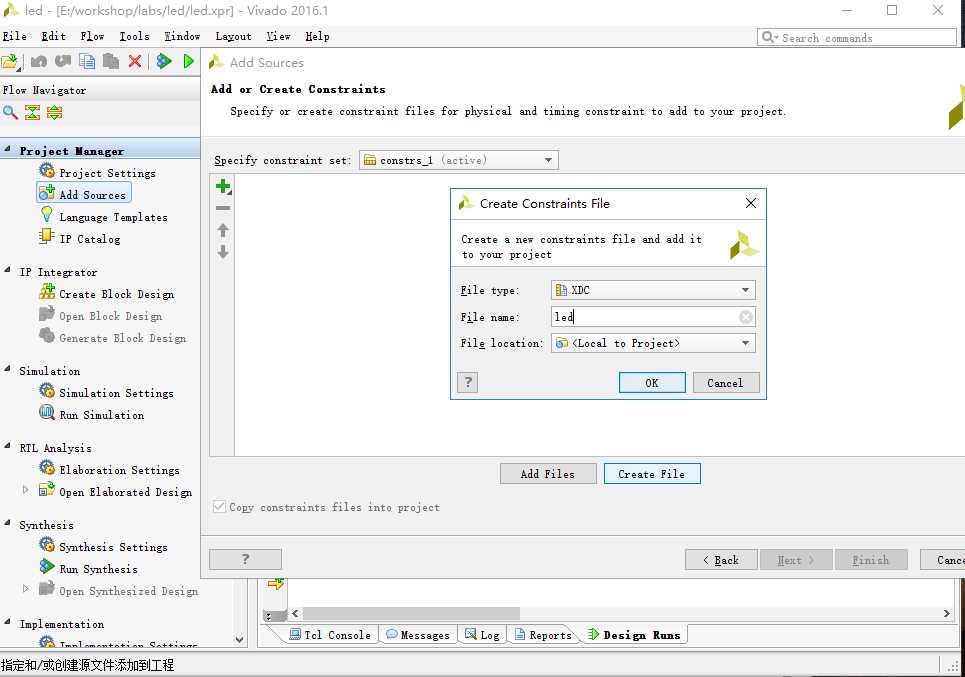

8.添加XDC管脚约束文件

XDC文件里主要是完成管脚的约束,时钟的约束,以及组的约束

第一步:新建约束文件

第二步:创造约束文件

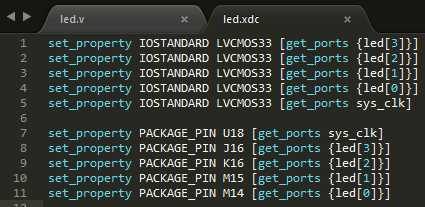

第三步:编辑管脚约束文件

其中,set_property PACKAGE_PIN “引脚编号” [get_ports “端口名称”]

Set_property IOSTANDARD “电压” [get_ports “端口名称”]

9.编译

第一步:运行Run Synthesis 综合

第二步:运行Run Implementation 布局布线

第三步:运行Generate Bitstream 生成bit文件

10.下载和调试

运行Hardware Manager。

原文:http://www.cnblogs.com/chensimin1990/p/6837122.html