每个GPIO端口有如下几个寄存器进行操作:

注:GPIO_BRR和GPIO_BSRR支持读写的原子访问

每组GPIO的 port可以配置成如下的IO方式:

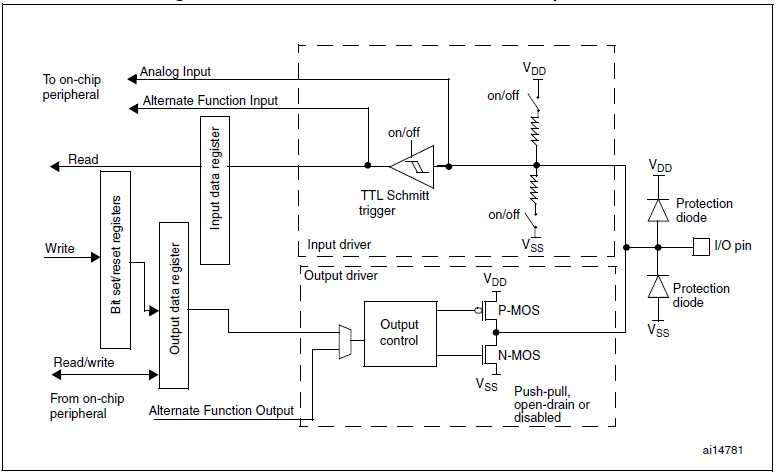

图 标准GPIO位的基本结构

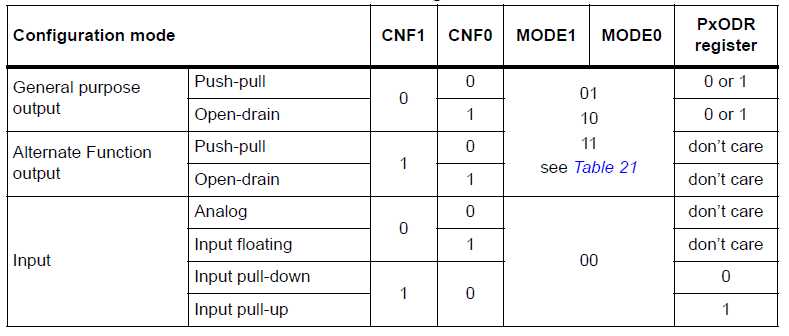

图 port bit配置表

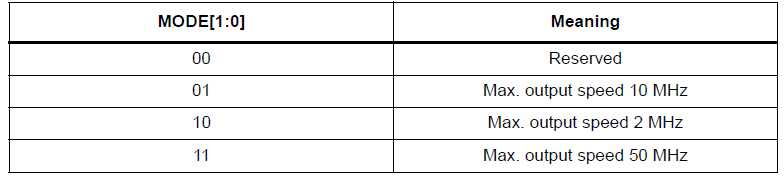

图 输出模式bit

引脚的可选功能是无效的,端口被配置成Input Floating Mode(CNFx[1:0]=01b, MODEx[1:0]=00b).

RESET后JTAG pin:PA15: JTDI in PU 、 PA14: JTCK in PD 、 PA13: JTMS in PU 、 PB4: NJTRST in PU

写到GPIOx_ODR中的值被输出到port引脚,可能使用的驱动模式:push-pull or open-drain

GPIOx_IDR在每个APB2时钟周期会捕获IO引脚上的数据

注:1.每个GPIO PIN都有一个弱上拉和一个弱下拉,在配置为输入模式时可以决定是否使能

在操作GPIO_ODR寄存器的时候没有必要关中断,通过写入GPIO_BRR或GPIO_BSRR来set或reset GPIO的相关port bit

STM32F103X datasheet学习笔记---GPIOs and AFIOs

原文:http://www.cnblogs.com/smartjourneys/p/7290720.html