复位可以说是FPGA逻辑开发中绕不开的一个基本问题,但不是每个人都能理清楚。常用的三种方式:

- 异步复位

- 同步复位

- 异步复位同步释放

这三者的优缺点网上有很多资料,特权同学的书里面也讲解的非常清楚。这三种写法的实现由什么区别呢,实际操作一遍理解会更深刻。

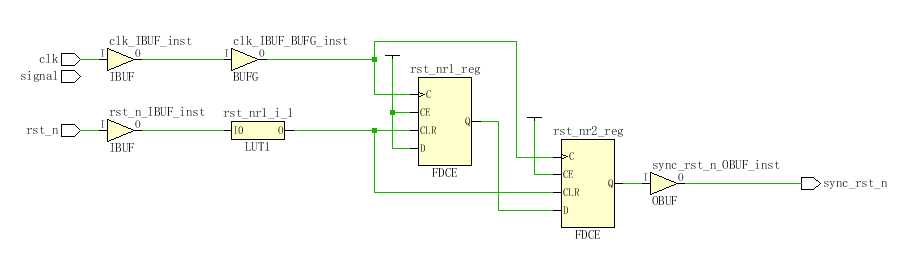

当然异步复位同步释放的方式最好,而且其实这点资源影响微乎其微,推荐还是使用这种方式。

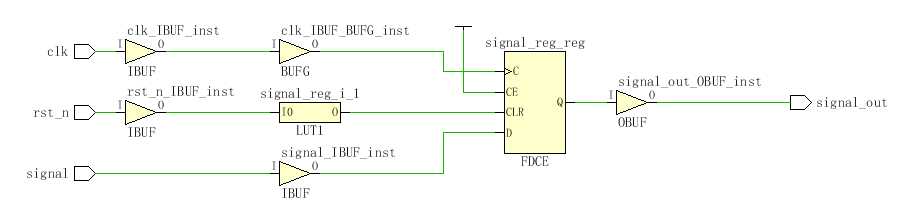

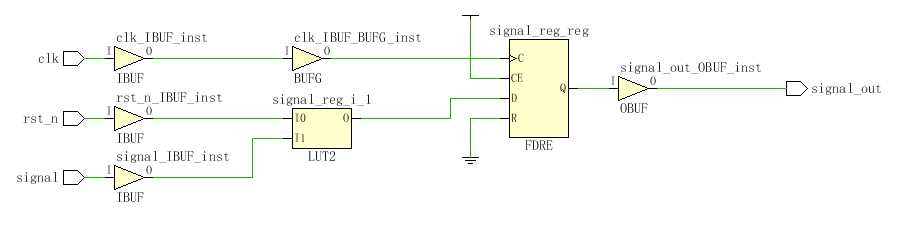

代码及综合后的电路:

异步复位

reg signal_reg; always@(posedge clk, negedge rst_n) begin if(!rst_n)begin signal_reg <= 0; end else begin signal_reg <= signal; end end

同步复位

reg signal_reg; always@(posedge clk) begin if(!rst_n)begin signal_reg <= 0; end else begin signal_reg <= signal; end end

异步复位同步释放

reg rst_nr1, rst_nr2; always@(posedge clk, negedge rst_n) begin if(!rst_n)begin rst_nr1 <= 0; rst_nr2 <= 0; end else begin rst_nr1 <= rst_n; rst_nr2 <= rst_nr1; end end assign sync_rst_n = rst_nr2;