在Verilog中,parameter既不属于变量范畴也不属于线网范畴,经常用来定义一个标志符代表一个常量,所以参数的值在仿真运行的过程中不能进行修改。但是通过使用参数,可以提高程序的可读性、可复用性和可维护性。目前常用的参数主要分为两大类:module参数(parameter和localparam)和specify参数(specparam)。

虽然参数使用起来较为方便,但是在使用参数时还需要注意以下几点:

【注意】

按照1364的描述,参数可以指定类型和范围,但是要遵守一定的规则:

【示例】

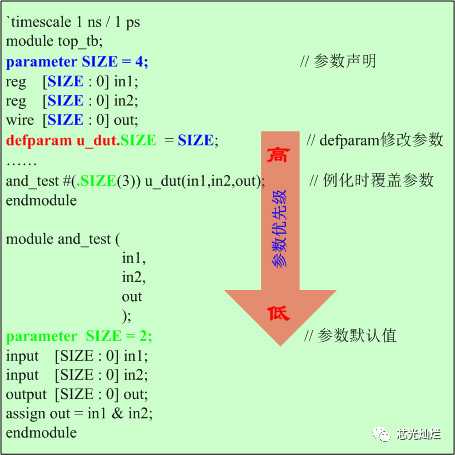

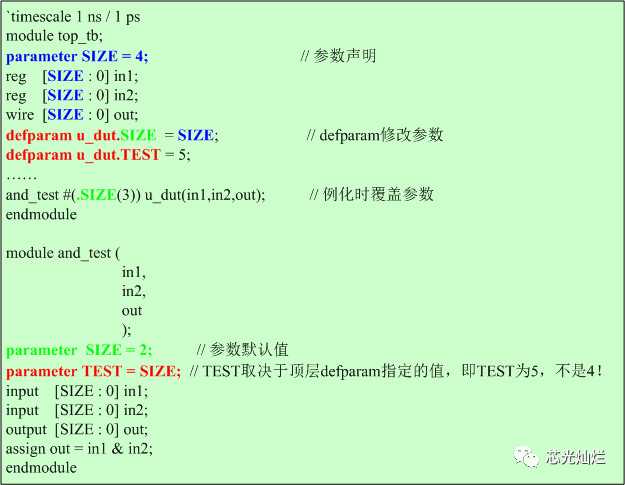

通过对上述代码的仿真,可以得到以下几个特点:

第三行声明的参数SIZE并没有指定数据类型和参数范围,所以在仿真时,SIZE的宽度默认为31位;

尽管在模块例化时,通过参数传递覆盖了模块中的参数SIZE,但是defparam通过层次路径覆盖设计中的参数具有更高的优先级(由此可以知道defparam的执行处于elaboration的最后阶段);

【注意】defparam可能在将来Verilog新的版本中删除,所以在设计中尽量不要使用。

localparam与parameter基本功能相同,两者的不同主要表现在以下几方面:

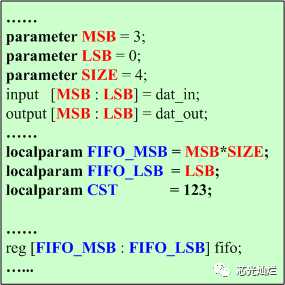

【示例】

上述代码中MSB和LSB均可以通过defparam和模块例化的方式进行修改,但是FIFO_MSB和FIFO_LSB仅能通过MSB、LSB、SIZE进行修改或者直接赋值为常量。也就是说,如果要对localparam进行重新修改,那么只能通过parameter间接的进行修改,其参数化是通过parameter体现的;

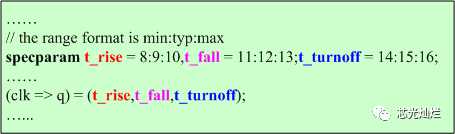

specparam声明了一种较为特殊的参数,除了不能赋值给parameter外,其可以出现在一个模块的任何位置,specparam指定的参数的声明必须先于其使用。与其他参数不同的是,specparam指定的参数不能在模块中通过例化或者参数传递进行修改,唯一可以修改参数肚饿方法是通过SDF反标修改;

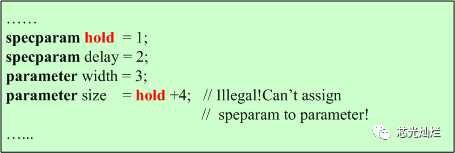

【示例】

通过上例,这里需要注意以下几点:

parameter不能被specparam指定的参数修改,否则编译将不会通过;

当specparam指定的是一个参数范围时,该参数将不能被修改!

三种参数的主要异同点如下表:

|

specparam参数 |

parameter参数 |

localparam参数 |

|

声明时关键词为specparam |

声明时关键词为parameter |

声明时关键词为localparam |

|

可在模块(module)内或specify块内进行声明 |

在specify块外,module中声明 |

在specify块外,module中声明 |

|

可在模块(module)内或specify块内使用 |

不能在specify块中使用 |

不能在specify块中使用 |

|

可以通过specparam或者parameter指定的参数赋值 |

不能被specparam指定的参数赋值 |

只能通过parameter参数赋值 |

|

常用于时序约束,在本模块中声明定义,用于specify块 |

常用于模块间参数传递,在本模块中声明定义 |

不可直接进行参数传递,在本模块中声明定义 |

|

可通过SDF反标修改指定的参数值 |

通过defparam或者模块例化修改原参数值 |

通过parameter修改原参数值 |

|

Specparam指定参数时,可以指定参数的取值范围,但是指定参数范围后改参数将不能被修改 |

不能指定参数的取值范围 |

不能指定参数的取值范围 |

通过defparam语句进行修改,但是通过该语句仅能修改parameter参数;

通过模块例化修改设计中的参数(参数传递的方式与端口信号传递方式类型:参数顺序隐实式传递和参数名显示传递),但是修改的对象也仅限于parameter参数,localparam只能通过parameter间接的被修改;

specparam只能通过SDF反标的方式被修改,且parameter不能赋值给specparam;

这里需要注意的是,如果模块中的参数在模块中取决于另一个参数,但是在顶层通过defparam对该参数进行了修改,那么改参数的最终值取决于defparam执行后赋予的值,不受其他参数影响;

【示例】

上例中虽然参数TEST被赋予了参数SIZE,但是最终实际上传递TEST的值取决于defparam指定的值。

更多资讯,请关注个人公众号:芯光灿烂

RTL基本知识:参数三姐妹-parameter-localparam-specparam

原文:https://www.cnblogs.com/xgcl-wei/p/9090918.html