jchdl:Jianchang Constructed Hardware Description Library,使用Java语言开发的硬件描述库。(Java是商标不让用,那就用名字 :-)

一. 设计目标

1.设计目标

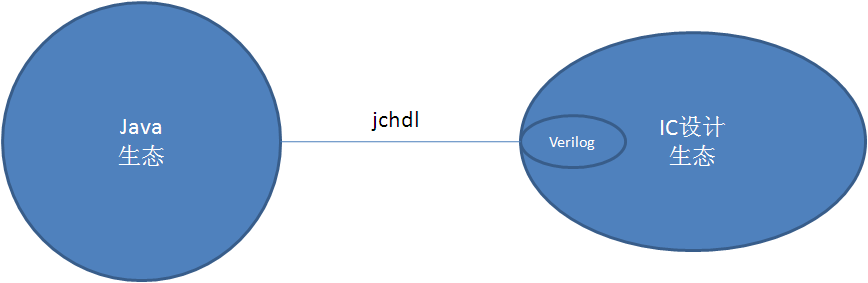

打通IC开发和Java生态,以Java生态的赋能IC开发。

2. 当前路径

当前的路径是基于Java语言,建立硬件建模库(library)。使用jchdl建立硬件模型之后,可以直接进行功能验证。然后转换为Verilog语言,使用现有的工具集对转换后的模型进行验证、仿真等。

? ?

?

3. 现实

现实是,目前只实现了很小一部分功能。请视该项目为抛砖引玉,希望借助社区的力量(IC专业领域和Java开发领域的专家)来完善。

4. LICENSE

该项目使用较为宽松的BSD 3-Clause License。 希望能够成为一块好砖。

二. 基于Java

a. Java语言是流行的面向对象编程语言(OOP)。

b. Java语言是跨平台的语言,基于Java语言的代码可以一次编译、到处运行。

c. Java语言是编程语言从近代走向现代的象征。

Java不只是Java语言,而是Java生态:

- 先进的并不断演进的编程理念。各种设计模式、架构,基于Java衍生出来。

- 开放的Java社区。基于Java的开源项目众多、层出不穷。Java社区奉行开放的文化,源源不断的产生各种开放的资源。相较之下,IC生态则由于较高的专业门槛,而在很大意义上是封闭的。

- 强大的工具支持。开发环境有Eclipse/Netbeans/Intellij IDEA等强大的工具,相较之下Verilog使用的vim和EDA编辑工具犹如处在石器时代。其他如UML建模工具可以实现建模之后直接转化为Java代码,代码结构可视化工具可以直接分析Java代码生成结构图等。

- 品类繁多且仍在不断增加的各种库:每一种库即是对一个方面的赋能。

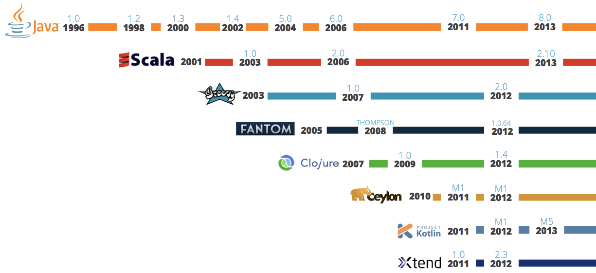

- 先进的Java虚拟机(JVM):JVM已经成为很多想要实现跨平台的语言的首选后端。很多新生的语言都是基于JVM设计,代码最终生成与Java一样的字节码(class)文件,供Java虚拟机解释运行。

? ?

?

三. 当前实现

由于时间和能力限制,目前仅实现了如下功能:

- 门和开关层(GSL)建模模型,可以基于建模方法论(Methodology)进行建模(model a hardware model);

- 门和开关层(GSL)模型验证,可以直接运行查看运行结果进行验证;

- RTL层模型验证,可以直接运行查看运行结果进行验证;

二. 辅助建模

当前实现的功能有限,没有建模等后续阶段的支持,所以当前只能进行辅助建模。

三. 模型验证

验证原理:

- GSL模型验证,基于值的传播。值的变化在线和节点上进行传播,如果值没有变化则不会进行传播(可以避免拓扑中的环导致的死循环)。

- RTL模型验证,基于事件驱动模型,参考Verilog event schedule机制。当有wire或reg的值变化,而又有依赖这个reg和wire的逻辑时,则执行这段逻辑。逻辑的执行又导致新的事件产生。在一个time slot中,一直执行,直到没有新的事件产生为止。

验证方法:

- 使用Intellj IDEA等IDE提供的断点功能,在执行时停下来观察变量的值。也可以单步执行、步入、步出等功能跟踪代码执行流程。

- 使用log机制,记录执行过程中的log,执行完成之后再行分析。

数字电路建模 - jchdl

原文:https://www.cnblogs.com/wjcdx/p/9607530.html