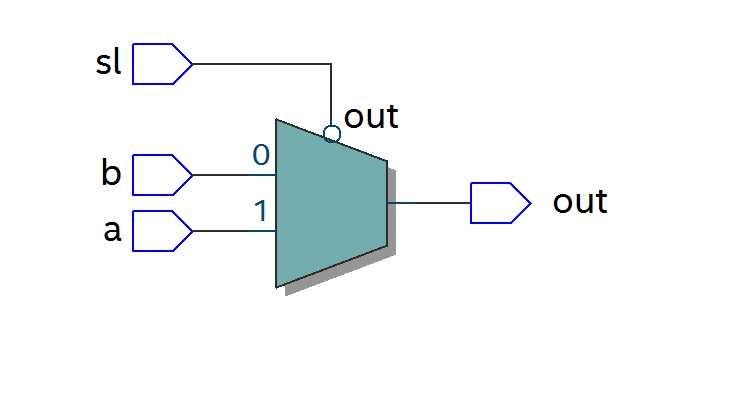

一个简单的二选一多路选择器

逻辑图

Verilog源程序

module Mux_Two ( input a, //Data input b, //Data input sl, //High: b ;Low: a output reg out ); always@(sl or a or b) if(!sl) out=a; else out=b; endmodule

Modelsim架构文件

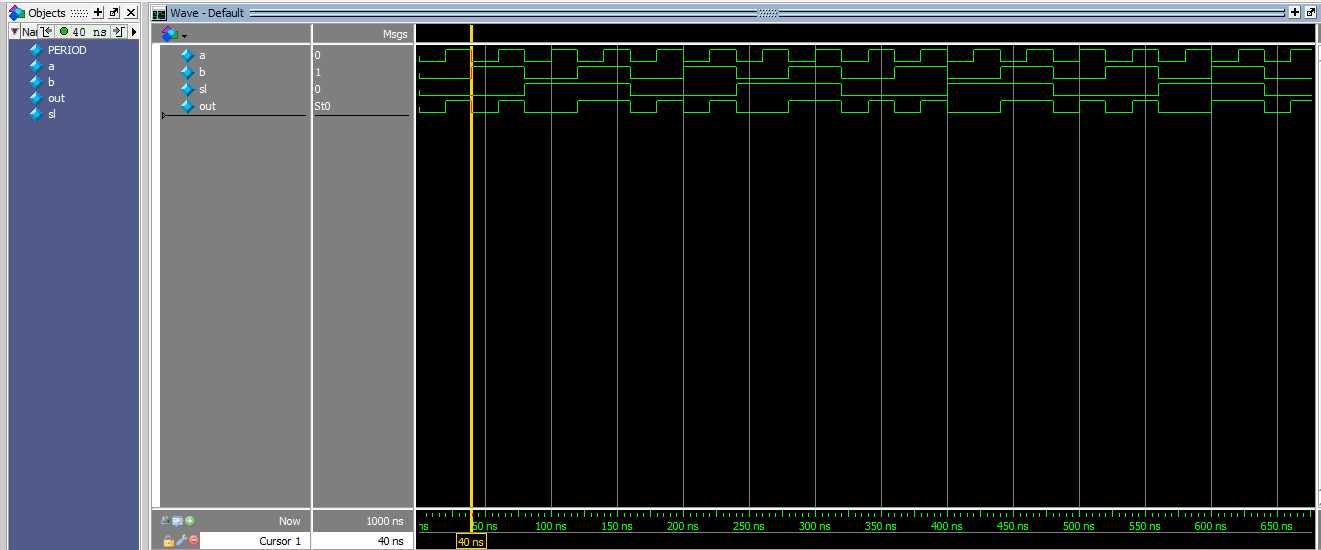

a为输入25MHz方波,b为输入12.5MHz的方波,sl为输入6.25MHz的方波。sl为高电平时,out输出b;sl为低电平时,out输出a。

`timescale 1ns/1ns module Mux_Two_TB; localparam PERIOD=20; reg a; //25Mhz reg b; //12.5Mhz wire out; //6.25Mhz reg sl; //High: b ;Low: a initial begin a=0; forever #(PERIOD) //25Mhz a=~a; end initial begin b=0; forever #(PERIOD*2) //12.5Mhz b=~b; end initial begin sl=0; forever #(PERIOD*4) //6.25Mhz sl=~sl; end Mux_Two u_Mux_Two ( .a (a), .b (b), .sl (sl), //High: b ;Low: a .out (out) ); initial begin end endmodule

仿真结果

原文:https://www.cnblogs.com/CrazyStranger/p/9662752.html