Quartus II综合器对于使能信号的产生

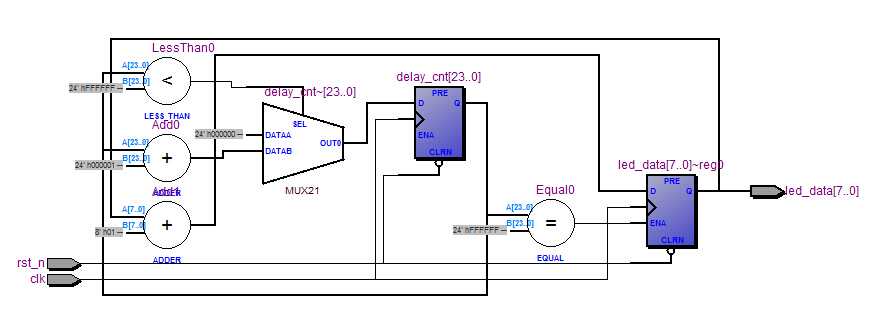

对比下面的代码和综合结果(代码取自crazybingo例程):

always@(posedge clk or negedge rst_n) begin if(!rst_n) delay_cnt <= 0; else if(delay_cnt < DELAY_TOP) delay_cnt <= delay_cnt + 1‘b1; else delay_cnt <= 0; end wire delay_done = (delay_cnt == DELAY_TOP) ? 1‘b1 : 1‘b0; //----------------------------------- always@(posedge clk or negedge rst_n) begin if(!rst_n) led_data <= 0; else if(delay_done) led_data <= led_data + 1‘b1; else led_data <= led_data; end

产生使能信号的两个必要条件是:

1. 必须对触发输出的信号进行条件信号(使能信号)的判定。

2. 必须保证条件信号的判定为假时触发器输出为前一状态的输入(即保持不变)。

这就是代码中两个if语句综合结果不一样的原因,上面的always块语句不能产生触发器使能信号,地下的块语句能够产生,因为它的逻辑符合使能信号的作用情况。

以下是上述代码综合后的RTL寄存器传输级电路图:

原文:http://www.cnblogs.com/Crazy-MFJ/p/3881130.html