1. 输入输出系统概述

- 组成:外设、接口、总线、管理软件

- 基本功能

- 完成计算机内外的信息传递

- 保证CPU正确选择输出设备

- 利用缓冲等,实现主机与外设的速度匹配

- 特点:异步性、实时性、设备无关性

- 输入过程:CPU把地址值放入总线 --> CPU等候设备数据有效 --> CPU从总线读入数据存入寄存器

- 输出过程:CPU把地址值放入总线 --> CPU把数据值放入总线 --> 设备等数据有效取走数据

- IO系统性能:存储IO、通信IO

- 连接特性:哪些设备可以和IO相连

- IO系统容量:IO系统可以容纳的设备数

- 响应时间:从用户输入命令到得到结果所花的时间(s)

- 吞吐率:单位时间完成的IO操作次数(用IOP表示)

2. 输入输出方式

- 无条件IO方式:执行IO指令时,CPU默认外设已经准备就绪,外设很难满足这一点

- 程序控制IO方式:执行IO指令时,先获取设备状态(设备状态寄存器),决定下一步操作(程序决定)

- 数据要经过CPU,CPU还要浪费大量时间查询设备状态

- 中断IO方式:外设主动通知CPU接收或输出数据,有实时性

- DMA方式:由硬件执行IO,外设准备好后通知DMA,DMA接管总线,完成数据交换

- 通道和IO处理机方式:外设种类很多速度差别很大,将外设管理工作从CPU总分离出来

- 通道本身就是个简单的CPU,执行IO指令的处理机

- IO处理机是通道的进一步发展,更像一个CPU了

3. 中断请求与响应

- 概念:CPU由内部外部事件引起CPU中断正在运行的程序,具有随机性(符合输入输出系统特性)

- 作用:主机与外设并行;故障处理;实时处理

- 类型:

- 内部中断(软件、异常)

- 外部中断(可屏蔽中断INTR、不可屏蔽中断NMI)

- 基本功能:

- 中断信号的保持与清除:通过寄存器存起来,处理完清零

- 中断优先级:硬件响应优先序、软件服务优先序(中断服务程序开头,设置自己的中断屏蔽位)

- 中断源识别:系统分配给每个中断源的代号(中断号),中断号获取可以用硬件或软件方式

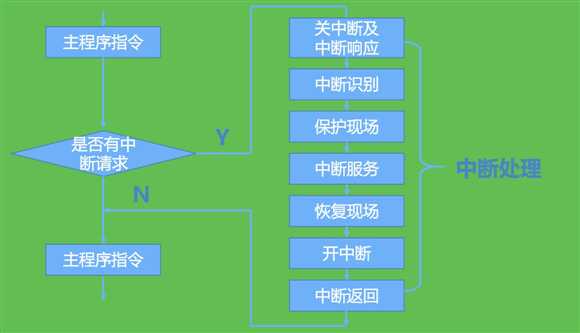

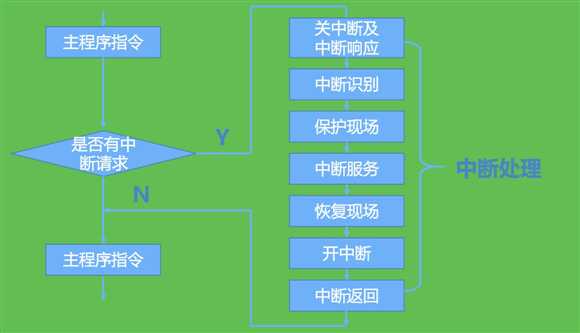

- 中断处理:

- 响应:每执行完一条指令,就会判断是否有中断请求

- 处理:保存断点(返回地址)、执行中断程序、返回断点

- 中断控制:

- 中断触发方式:指外设以什么逻辑信号去申请中断(边沿触发、电平触发)

- 中断排队方式:按优先级、循环轮流排队

- 中断嵌套:中断正在执行的中断程序,不可屏蔽中断不能嵌套

- 中断屏蔽:处理器内部有个触发器,“1”时才会响应外部中断

4. DMA方式

- 原理:数据传送不经过CPU,由DMA控制器实现内存和外设、外设和外设之间的直接快速传递

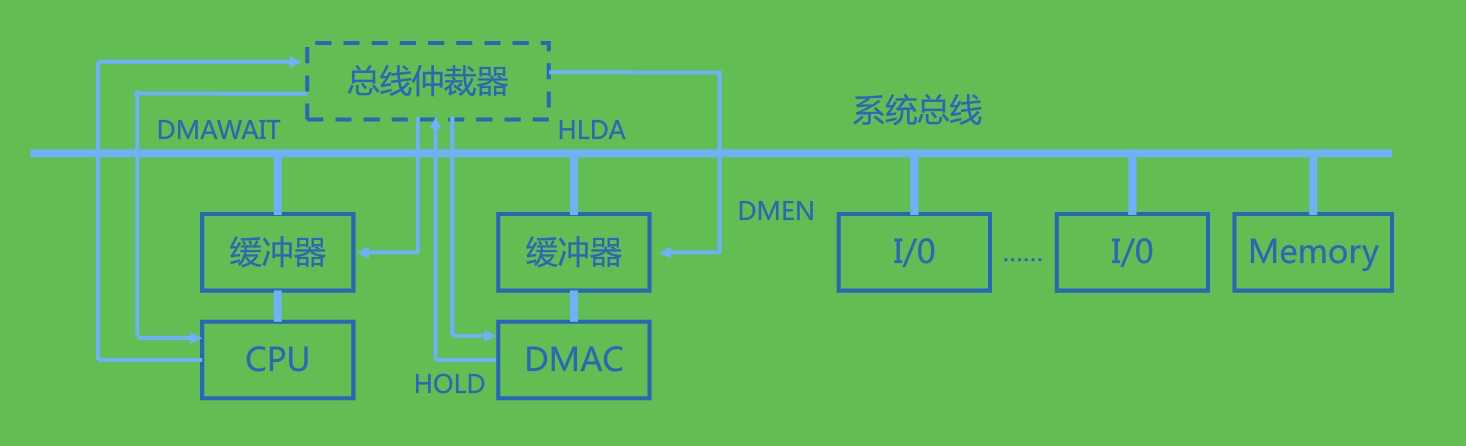

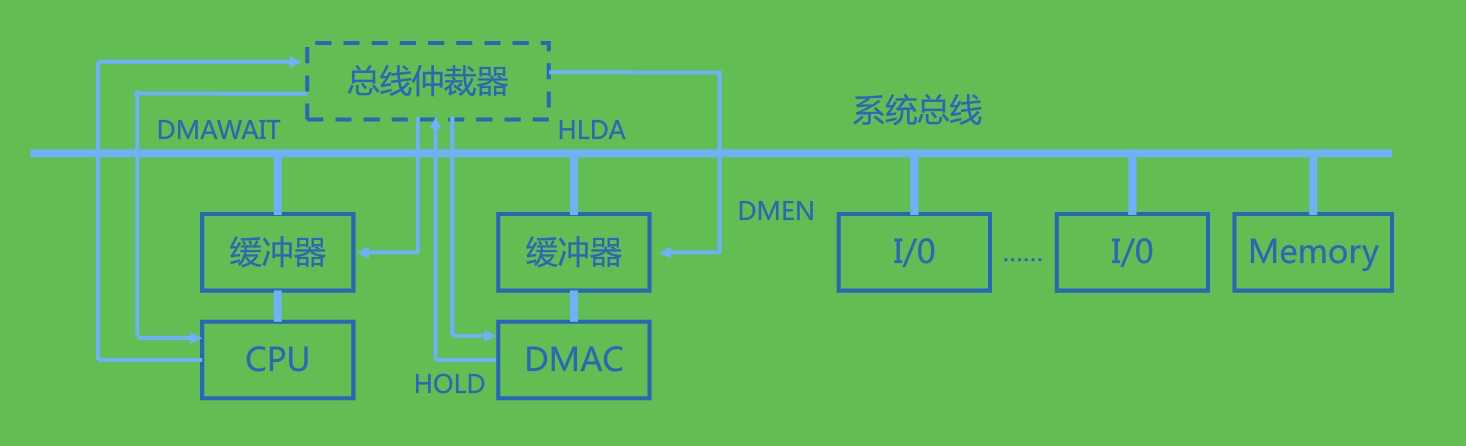

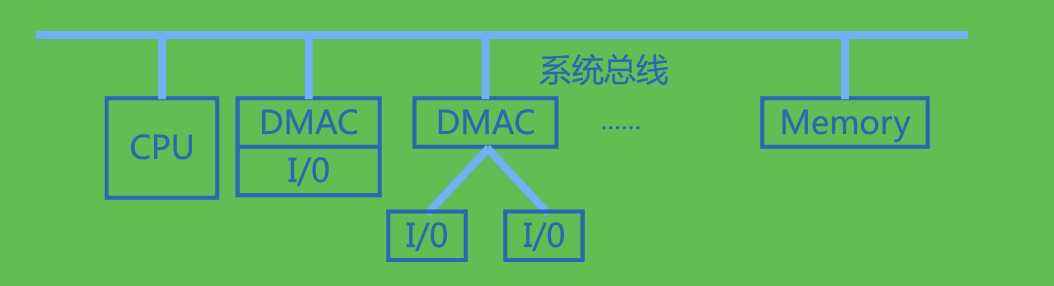

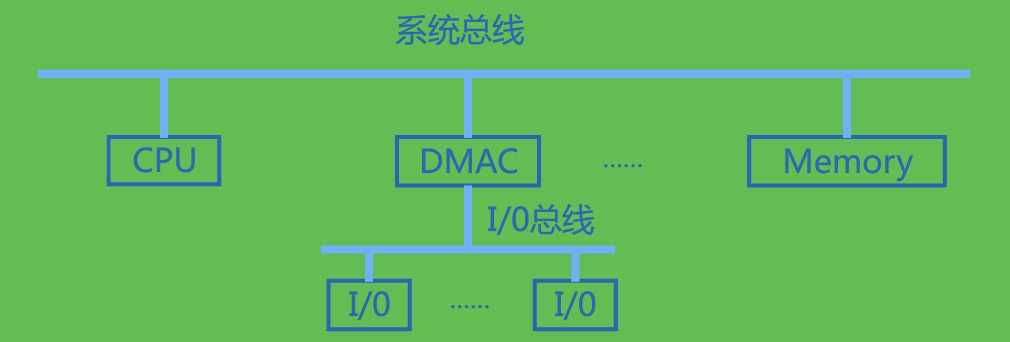

- 系统构成:

- DMA作为主设备之一

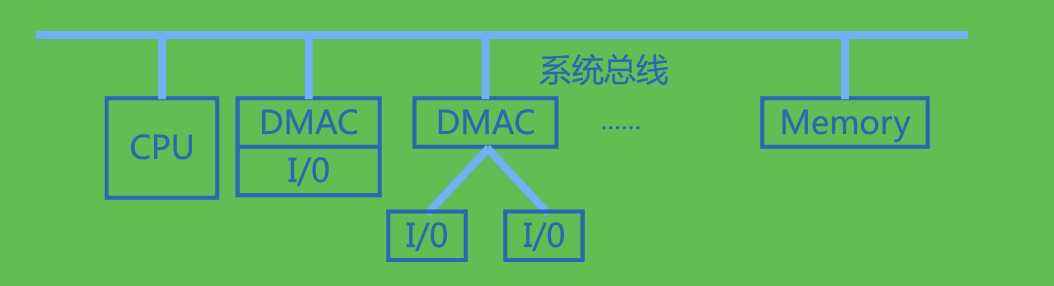

- DMA与IO接口集成

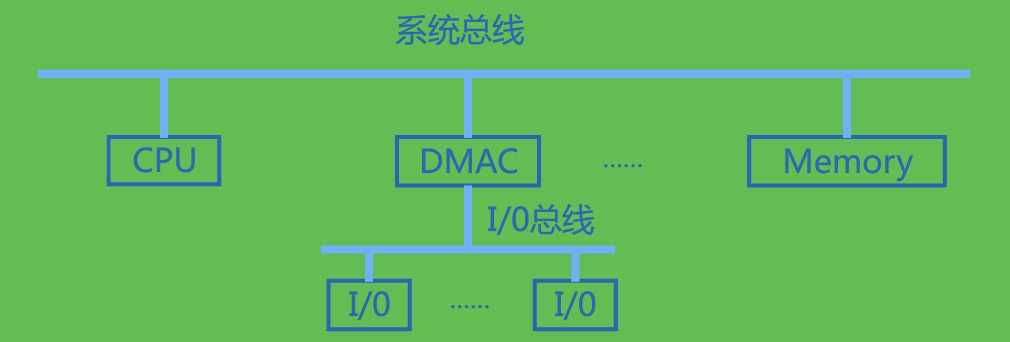

- DMA提供专门IO总线

- DMA的两种工作状态:被动态(未获得总线控制权,受CPU控制)、主动态(获得总线控制权)

- 传输步骤:

- 申请:一个设备接口试图通过总线向另一个设备发送数据,先向CPU发送DMA信号

- 响应:CPU收到DMA信号,当前总线周期结束后,按DMA信号优先级响应相应的DMA控制器

- 数据传送:DMA收到CPU响应,获得总线控制权,开始直接数据传送

- 传送结束:设备向CPU发送DMA结束信号,交换总线控制权

- DMA操作类型:

- 数据传送:源地址数据传到目的地址

- 数据校验:不传输,只校验某数据块内部的每个字节

- 数据检索:不传输,只在制定内存区域内查找某个关键字或某几个数据位是否存在

- DMA操作方式:

- 单字节传输模式:每次DMA操作传送一个字节

- 块传输模式:每次传送多个字节,有个当前字节计数器,+1 +1 +1

- 请求传输模式:DMA控制器询问外设,当外设请求信号无效时,暂停传输(不释放总线);再次有效再继续传输

- 级联传输模式:多个DMA级联,分布式

- DMA传输模式:

- 停止CPU访问内存:传输速率高的设备传输时有优势

- 周期挪用:DMA挪用一个或几个内存周期。若此时CPU不需要访存则不冲突,若冲突则DMA优先

- DMA与CPU交替访存:直接交替访存,不需要浪费时间

【重学计算机】机组D8章:输入输出系统

原文:https://www.cnblogs.com/flashsun/p/10626523.html