?

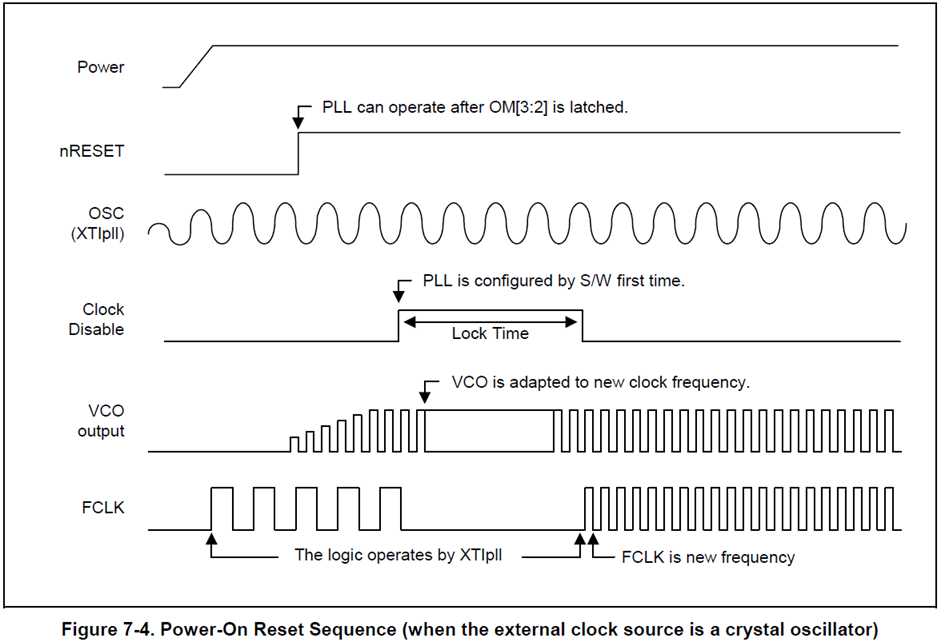

对Figure7-4的说明:

上电时,PLL没被启动,FCLK等于外部输入时钟,称为Fin。

1 上电几毫秒后,晶振(OSC)输出稳定,FCLK = Fin,nRESET恢复高电平后,CPU开始执行指令。

2 设置MPLL,等待Lock Time(使MPLL输出稳定),MPLL稳定输出,CPU工作于新的工作频率(在Lock Time期间,FCLK停震,CPU停止工作)。

?

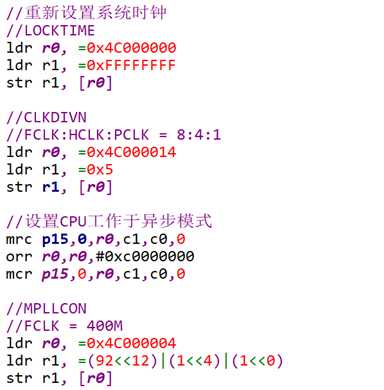

具体的配置的步骤:

1 设置Lock Time;

2 设置时钟比例(FCLK:HCLK:PCLK);

3 如果CLKDIVN寄存器的位HDIVN非0,CPU的总线模式应该从"fast bus mode"变为"asynchronous bus mode"; 如果位HDIVN非0,而CPU的总线模式仍是"fast bus mode",则CPU的工作频率将自动变为HCLK,而不是FCLK。

#MMU_SetAsynchronousBusMode

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_Nf:OR:R1_iA(#0xc0000000)

mcr p15,0,r0,c1,c0,0

4 设置MPLL;一旦设置MPLL,就会锁定Lock Time,直到MPLL输出稳定。

?

示例代码:

原文:https://www.cnblogs.com/lilto/p/10889212.html