ISE 生成PCIe核之后, 在ipcore_dir目录下会产生以下文件目录

具体目录树如下:

1 myPCIe 2 │ s6_pcie_readme.txt 3 │ 4 ├─doc 5 │ s6_pcie_ds718.pdf 6 │ s6_pcie_ug654.pdf 7 │ 8 ├─example_design 9 │ pcie_app_s6.v 10 │ PIO.v 11 │ PIO_32_RX_ENGINE.v 12 │ PIO_32_TX_ENGINE.v 13 │ PIO_EP.v 14 │ PIO_EP_MEM.v 15 │ PIO_EP_MEM_ACCESS.v 16 │ PIO_TO_CTRL.v 17 │ xilinx_pcie_1_1_ep_s6.v 18 │ xilinx_pcie_1_lane_ep_xc6slx45t-fgg484-2.u 19 │ 20 ├─implement 21 │ implement.bat 22 │ implement.sh 23 │ xst.prj 24 │ xst.scr 25 │ 26 ├─simulation 27 │ ├─dsport 28 │ │ gtx_drp_chanalign_fix_3752_v6.v 29 │ │ gtx_rx_valid_filter_v6.v 30 │ │ gtx_tx_sync_rate_v6.v 31 │ │ gtx_wrapper_v6.v 32 │ │ pcie_2_0_rport_v6.v 33 │ │ pcie_2_0_v6_rp.v 34 │ │ pcie_brams_v6.v 35 │ │ pcie_bram_top_v6.v 36 │ │ pcie_bram_v6.v 37 │ │ pcie_clocking_v6.v 38 │ │ pcie_gtx_v6.v 39 │ │ pcie_pipe_lane_v6.v 40 │ │ pcie_pipe_misc_v6.v 41 │ │ pcie_pipe_v6.v 42 │ │ pcie_reset_delay_v6.v 43 │ │ pcie_upconfig_fix_3451_v6.v 44 │ │ pci_exp_usrapp_cfg.v 45 │ │ pci_exp_usrapp_com.v 46 │ │ pci_exp_usrapp_pl.v 47 │ │ pci_exp_usrapp_rx.v 48 │ │ pci_exp_usrapp_tx.v 49 │ │ xilinx_pcie_2_0_rport_v6.v 50 │ │ 51 │ ├─functional 52 │ │ board.f 53 │ │ board.v 54 │ │ isim_cmd.tcl 55 │ │ simulate_isim.bat 56 │ │ simulate_isim.sh 57 │ │ simulate_mti.do 58 │ │ simulate_ncsim.sh 59 │ │ simulate_vcs.sh 60 │ │ sys_clk_gen.v 61 │ │ sys_clk_gen_ds.v 62 │ │ wave.do 63 │ │ wave.sv 64 │ │ wave.tcl 65 │ │ wave.wcfg 66 │ │ 67 │ └─tests 68 │ tests.v 69 │ 70 └─source 71 gtpa1_dual_wrapper.v 72 gtpa1_dual_wrapper_tile.v 73 myPcie.v 74 pcie_brams_s6.v 75 pcie_bram_s6.v 76 pcie_bram_top_s6.v

其中除了doc中包含了iP核相关文档,主要还包括以下两方面的内容

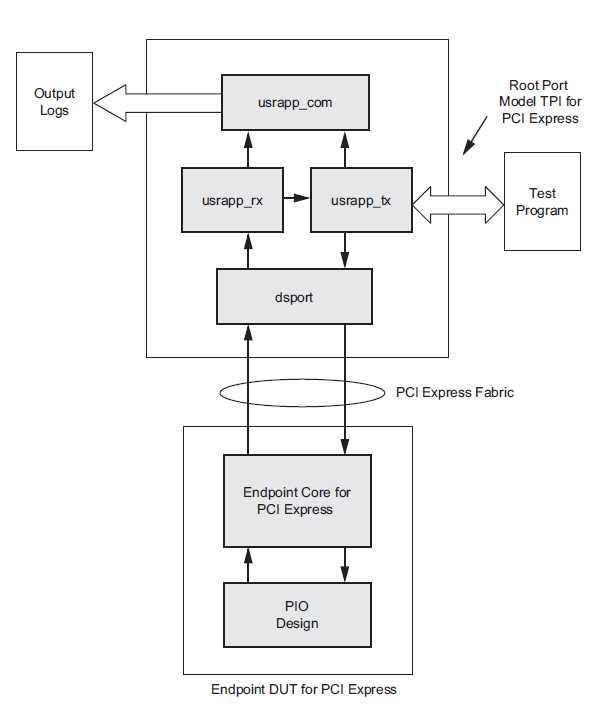

The example simulation design consists of two discrete parts:

用户可以通过root port model来仿真实现PCIe事务层的操作,并通过相应的数据收发模块实现对PCIe功能的仿真。Root Port Model包含以下功能

Root Port Model仿真模块和PCIe PIO设计的耦合关系如图所示

原文:http://www.cnblogs.com/zhongzhe/p/3906789.html