/*

--VGA Timing

--Horizontal :

-- ______________ _____________

-- | | |

--_______________| VIDEO |_______________| VIDEO (next line)

--___________ _____________________ ______________________

-- |_| |_|

-- B <-C-><----D----><-E->

-- <------------A--------->

--The Unit used below are pixels;

-- B->Sync_cycle :H_sync_cycle

-- C->Back_porch :hori_back

-- D->Visable Area

-- E->Front porch :hori_front

-- A->horizontal line total length :hori_line

--Vertical :

-- ______________ _____________

-- | | |

--______________| VIDEO |_______________| VIDEO (next frame)

--

--__________ _____________________ ______________________

-- |_| |_|

-- P <-Q-><----R----><-S->

-- <-----------O---------->

--The Unit used below are horizontal lines;

-- P->Sync_cycle :V_sync_cycle

-- Q->Back_porch :vert_back

-- R->Visable Area

-- S->Front porch :vert_front

-- O->vertical line total length :vert_line

*////////////////////////////////////////////

////////////////////////

//parameter

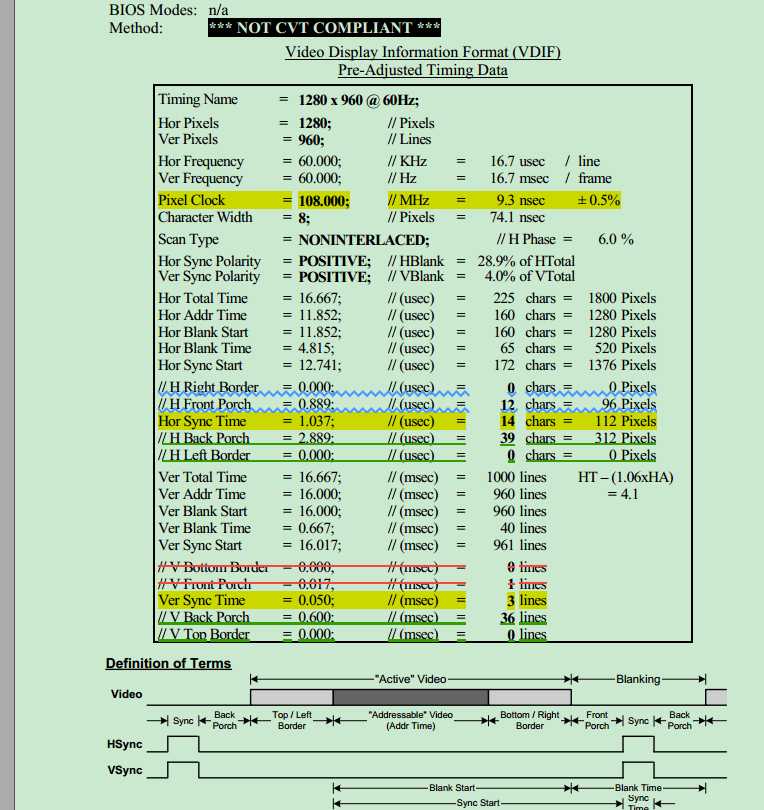

parameter hori_line = 1800; //Hor Total Time

parameter hori_back = 312; //Hor Blank Time 312+0

parameter hori_front = 96; // 96+0

parameter vert_line = 1000; //Ver Total Time

parameter vert_back = 36; // 36+0

parameter vert_front = 1; // 1+0

parameter H_sync_cycle = 112;//Hor Sync Time

parameter V_sync_cycle = 3; //Ver Sync Time

VESA-ADV7123-SOCKIT-DE2115,布布扣,bubuko.com

原文:http://www.cnblogs.com/TFH-FPGA/p/3911805.html