本文转自:自己的微信公众号《集成电路设计及EDA教程》

《机器学习在IC设计中的应用(二)--根据GBA时序结果来预测PBA》

AOCV

AOCV全称:Advanced OCV,28nm及以下工艺节点开始逐渐使用的STA方法。与之前的OCV(设置全局的timing derate值)相比能显著降低时序分析的悲观程度,使得时序分析结果更加接近真实结果。

GBA与PBA

AOCV有两种模式,如下:

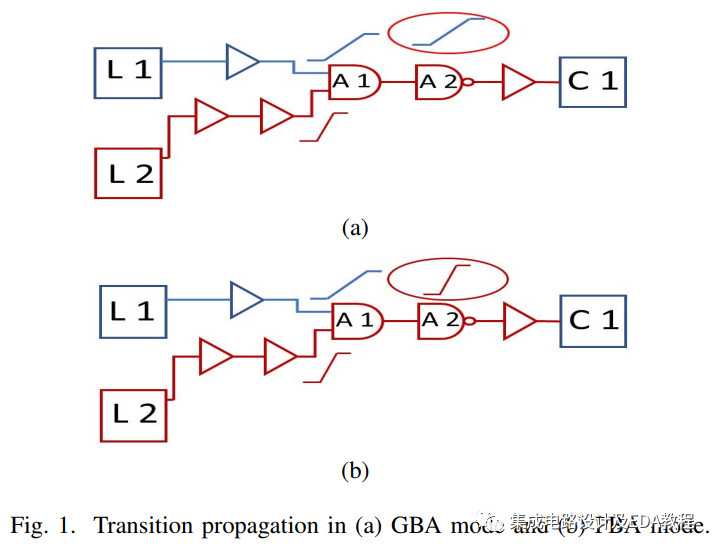

GBA (Graph-Based Analysis) : 一个Cell的delay,取多个输入的input transition的最差值去查表;

PBA (Path-Based Analysis):一个Cell的delay,不同path,分别按照input transition的真实值计算查表;

两者的区别如下图所示:

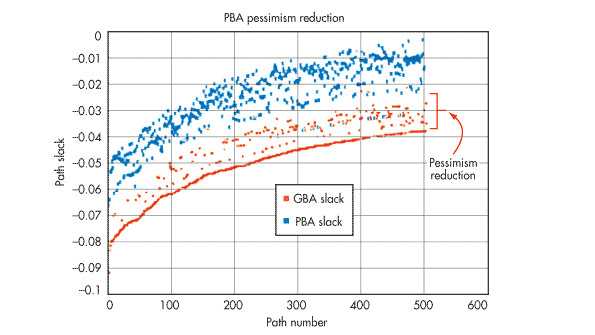

因此GBA的Timing会过于悲观,但是好处是计算保守,试想在最差情况下Timing如果满足的话,PBA mode下timing会更满足(如下图所示,GBA mode的包络线将所有PBA的点全部囊括在内)。

PBA mode与GBA mode相比,减少了分析的悲观程度,让分析结果更加接近真实的情况(现在的POCV等手段都是为了这个目的)。因此PBA mode的分析结果更加真实,一般用来Signoff timing用。

那你可能会问,PBA mode更加精确的话为什么还会去用GBA mode呢?

那是因为GBA mode有一个优点:计算速度快。

所以GBA和PBA是一个速度和精度的trade off。

下图给出了对数坐标下PBA与GBA模式下运行时间的比值,用的EDA工具是商用Signoff STA工具,工艺是28nm FDSOI。横坐标是设计的复杂程度,从4K flip-flop 40K个单元到 350K flip-flop 990K个单元。

从上图可知,随着设计复杂度的增加,PBA的运行时间的增加程度比指数增长还要快。

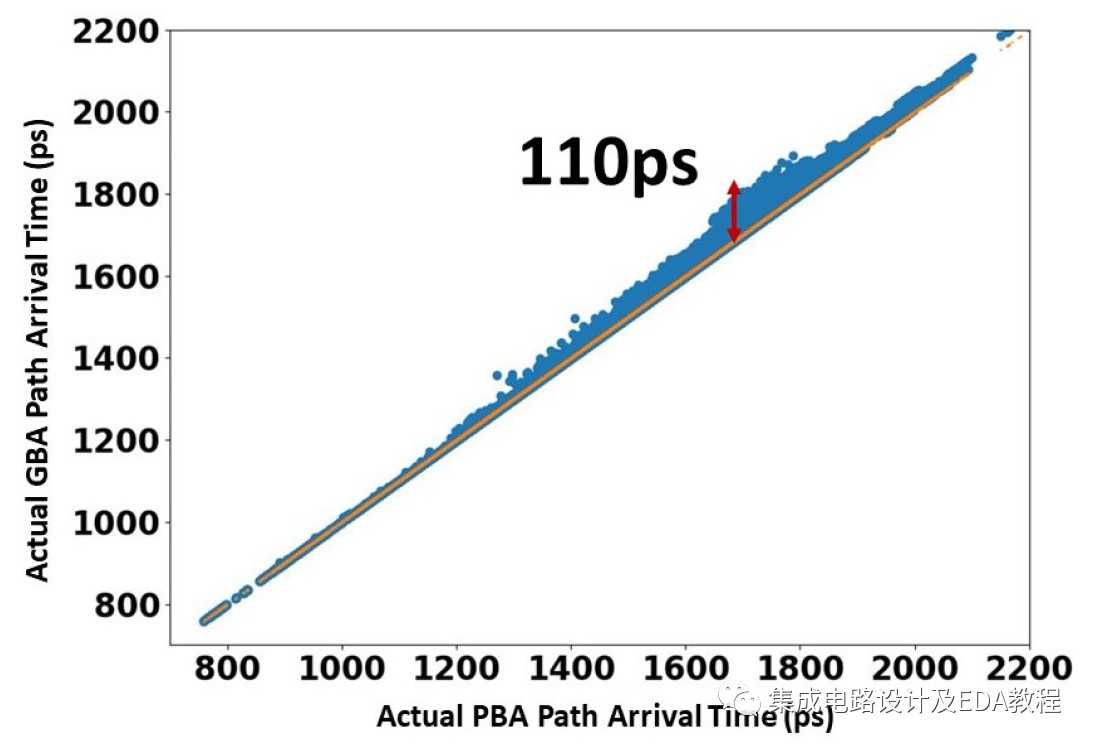

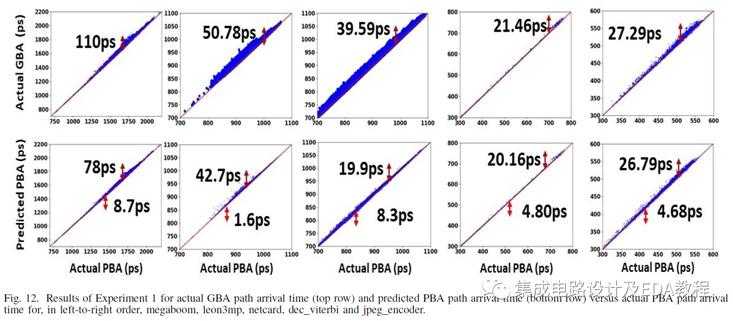

下图给出了GBA mode与PBA mode下两者在path arrival time上的对比结果,最差情况下偏差可达110ps。

那么问题来了,考虑到PBA mode运行时间的恐怖程度与GBA分析结果的悲观程度,有没有什么好的方法,能减小GBA的悲观程度,同时又不牺牲运行时间呢?这就是本推文要介绍的内容—如何基于GBA的timing结果去预测PBA timing?

实现思路

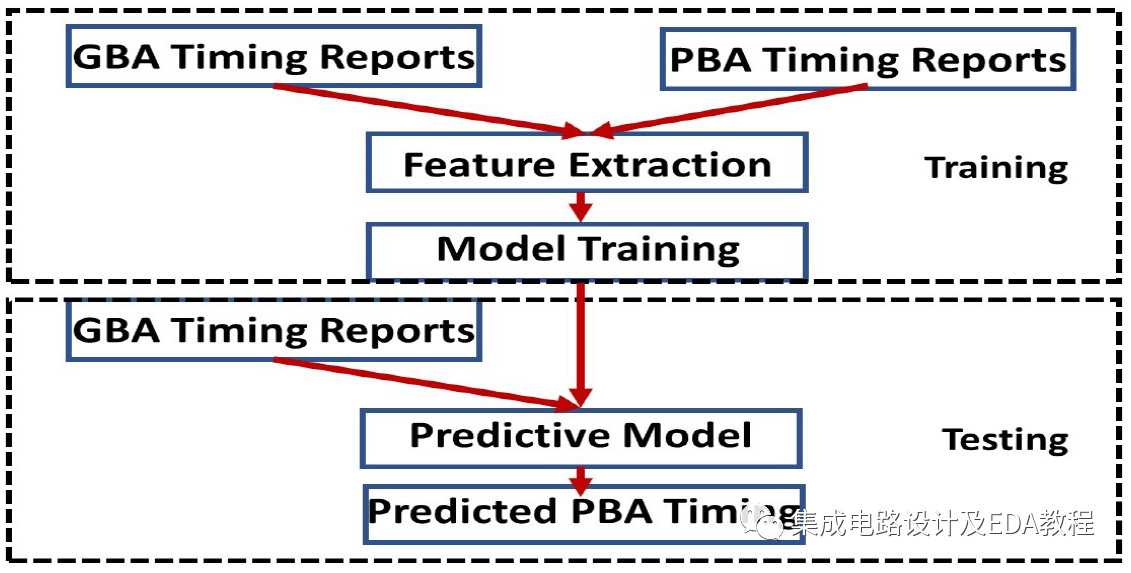

训练阶段:同时将GBA和PBA时序分析的结果作为特征提取和模型训练的输入对模型进行Training。

测试/应用阶段:

根据GBA时序分析的结果去预测PBA结果。

具体细节和算法见参考文献:

《Using Machine Learning to Predict Path-Based Slack from Graph-Based Timing Analysis》

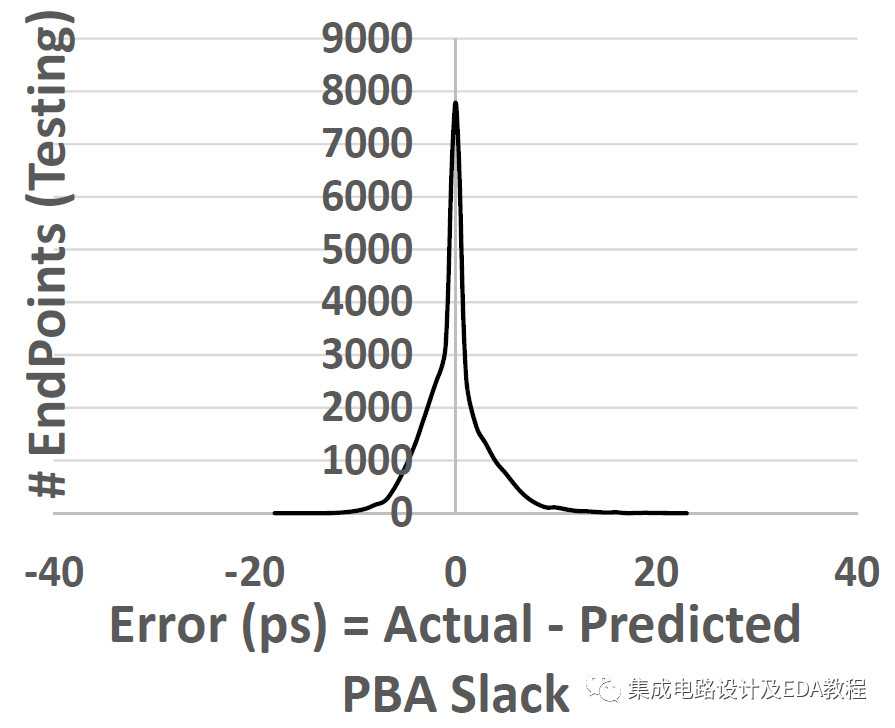

文章早期尝试了多元自适应回归样条(Multivariate Adaptive Regression Splines, MARS)模型。结果: 90%的endpoint的PBA slack预测值与PBA slack真实值之间偏差在5ps以内。如下图所示:

MARS介绍:

https://github.com/KeKe-Li/tutorial/blob/master/assets/src/RAM/RAM.0.4.md

从上图可以看出这种思路是可行的,且效果较好,但是该模型存在一些问题,文章提出了一个基于决策树和时序路径中stage bigrams电气和物理特征的模型。并取得了不错的结果。

结果

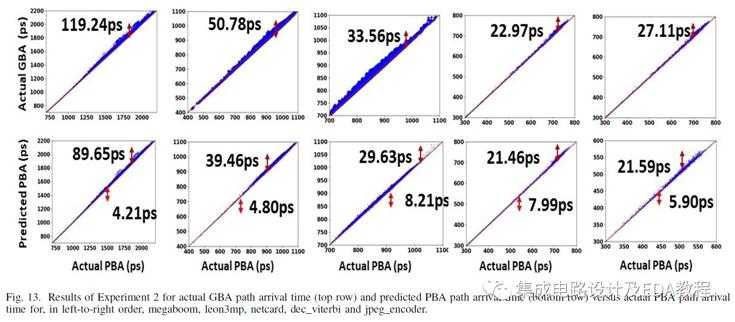

下图是真实的GBA/机器学习预测的PBA结果与真实的PBA结果的对比曲线:

从图中可以看出与传统的GBA分析结果相比,基于GBA和机器学习的方法在一定程度上降低了GBA模式的悲观程度,且与真实的PBA分析结果的线性度更高,GBA和PBA之间的结果离散程度比较大。虽然该成果的效果不是非常明显,但是思路非常新颖,扩展了我们的视野,相信以后在该方面会有更大的突破。

尾注

研究生阶段做过ML的算法和芯片,上述内容部分基于参考文献、已有的ML经验、IC设计经验,还有一些胡思乱想,哈哈哈,希望在脚踏实地做IC的同时也能采用一些大胆新颖的想法来让IC设计变得更有效率,把活儿干的更漂亮,同时让自己更加出色。

多分享,多点赞;

您的支持是我更新的动力,谢谢您的关注,更多资料请移步公众号《集成电路设计及EDA教程》

机器学习在IC设计中的应用(二)--根据GBA时序结果来预测PBA

原文:https://www.cnblogs.com/ASIC-Horizon/p/11182146.html