Zynq_soc学习

SFP高速串行通信得搞来看看

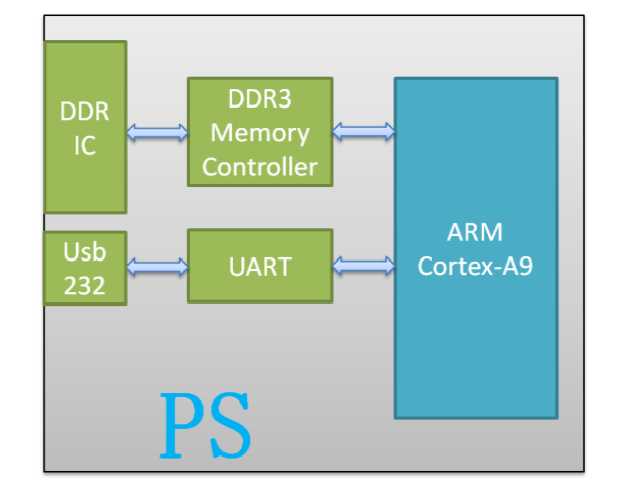

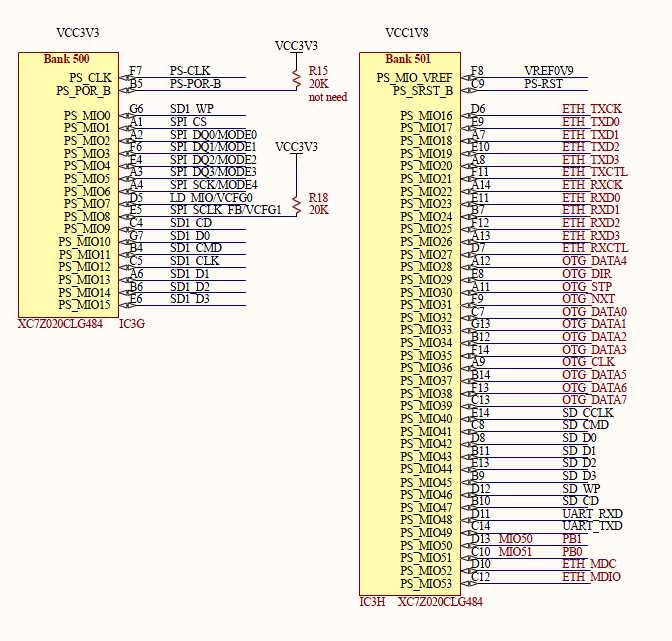

最小系统

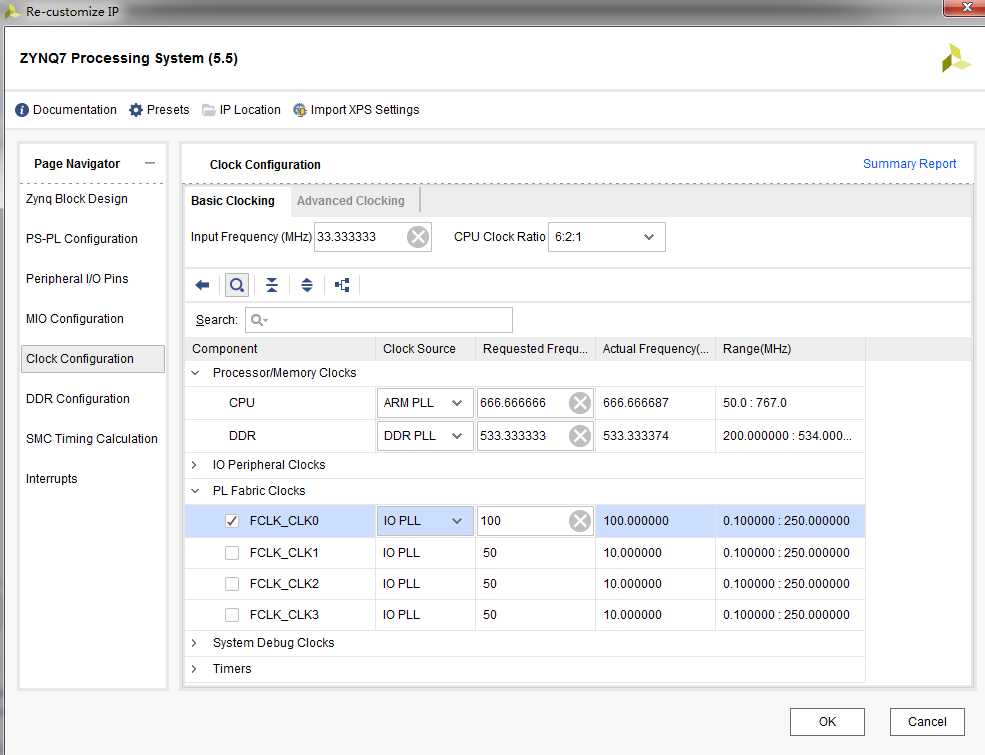

PL端时钟配置:

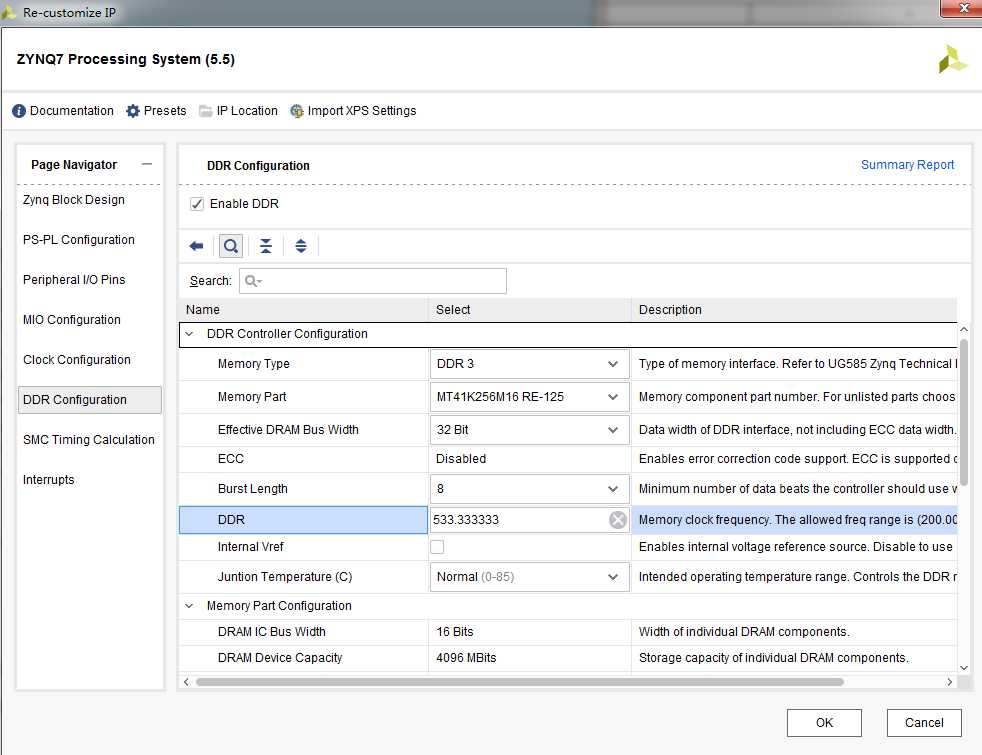

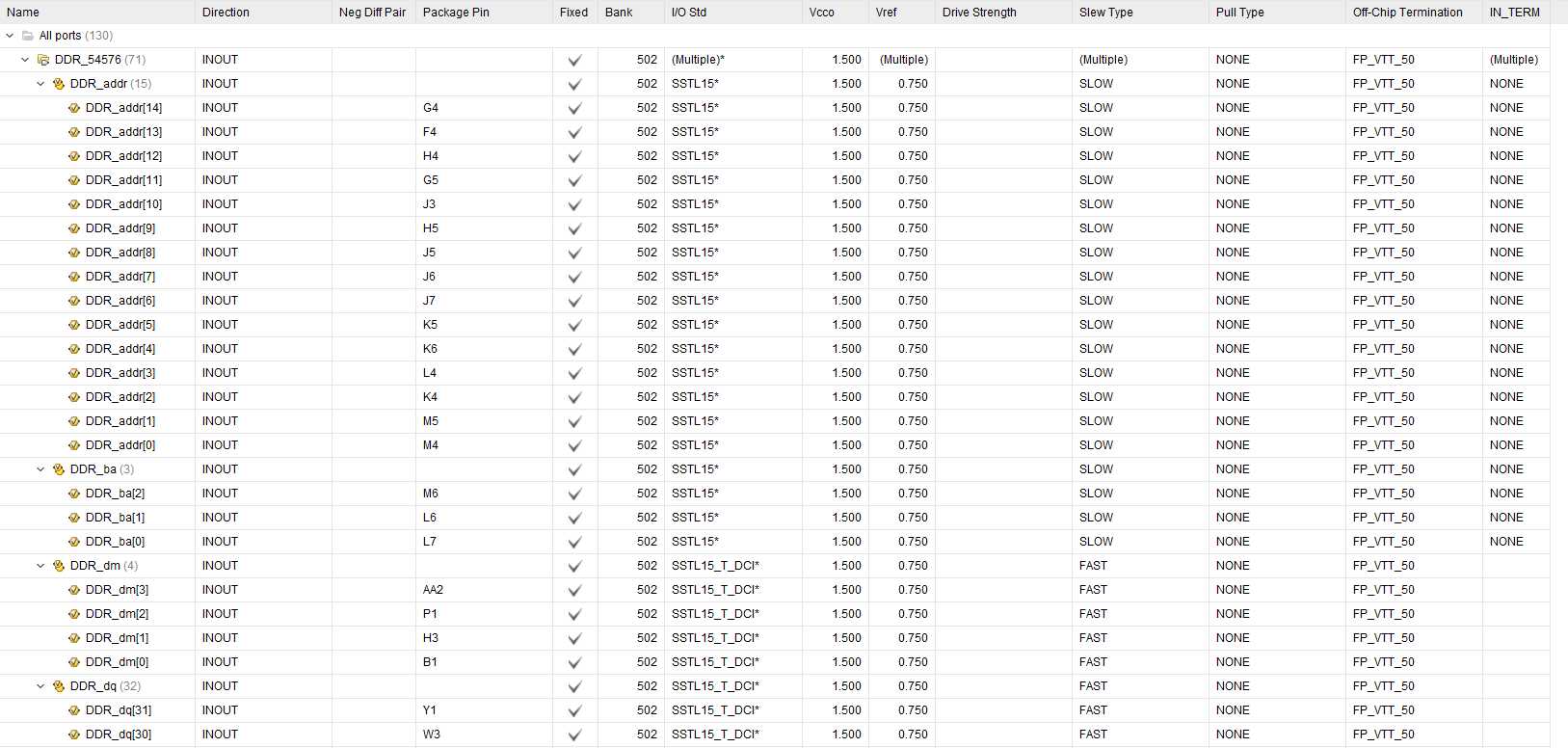

配置DDR控制器,主要是添加DDR正确的型号

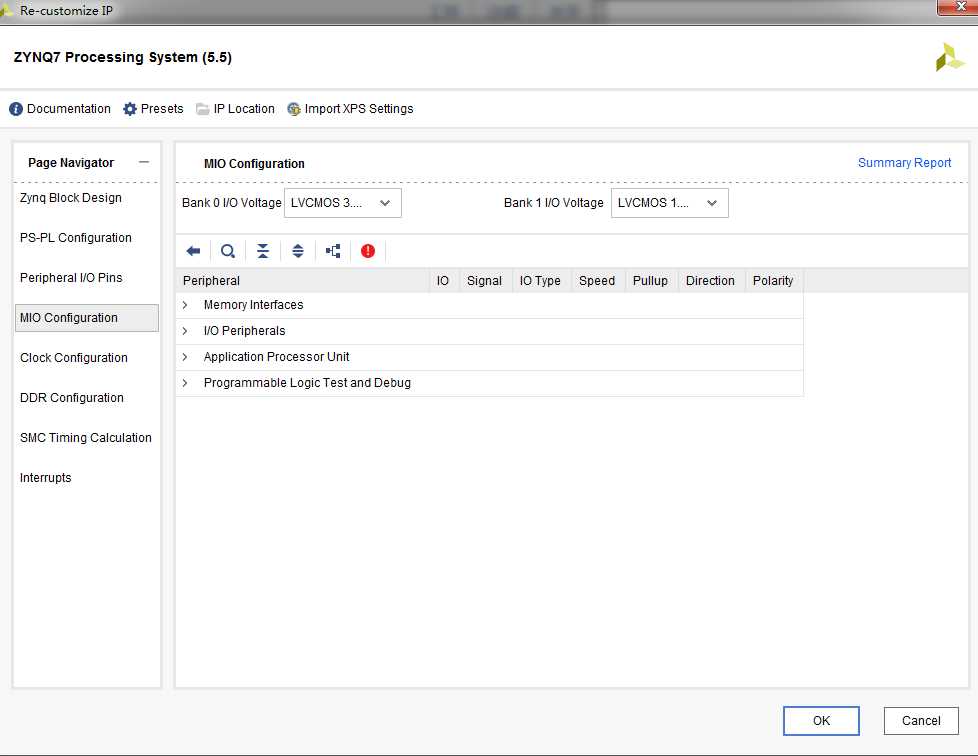

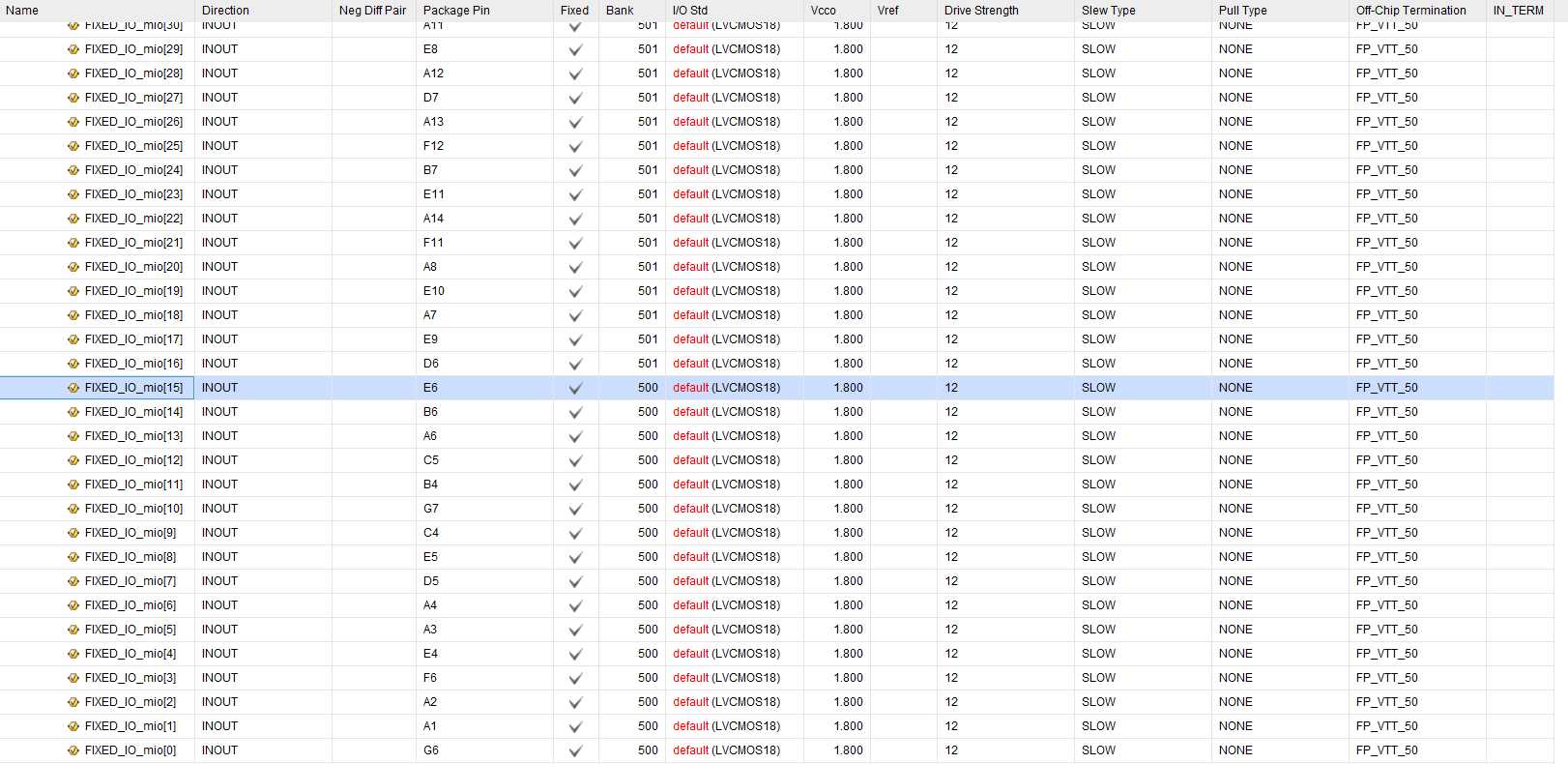

外设电平接口配置:

BANK0:LVCMOS3.3

BANK1:LVCMOS1.8

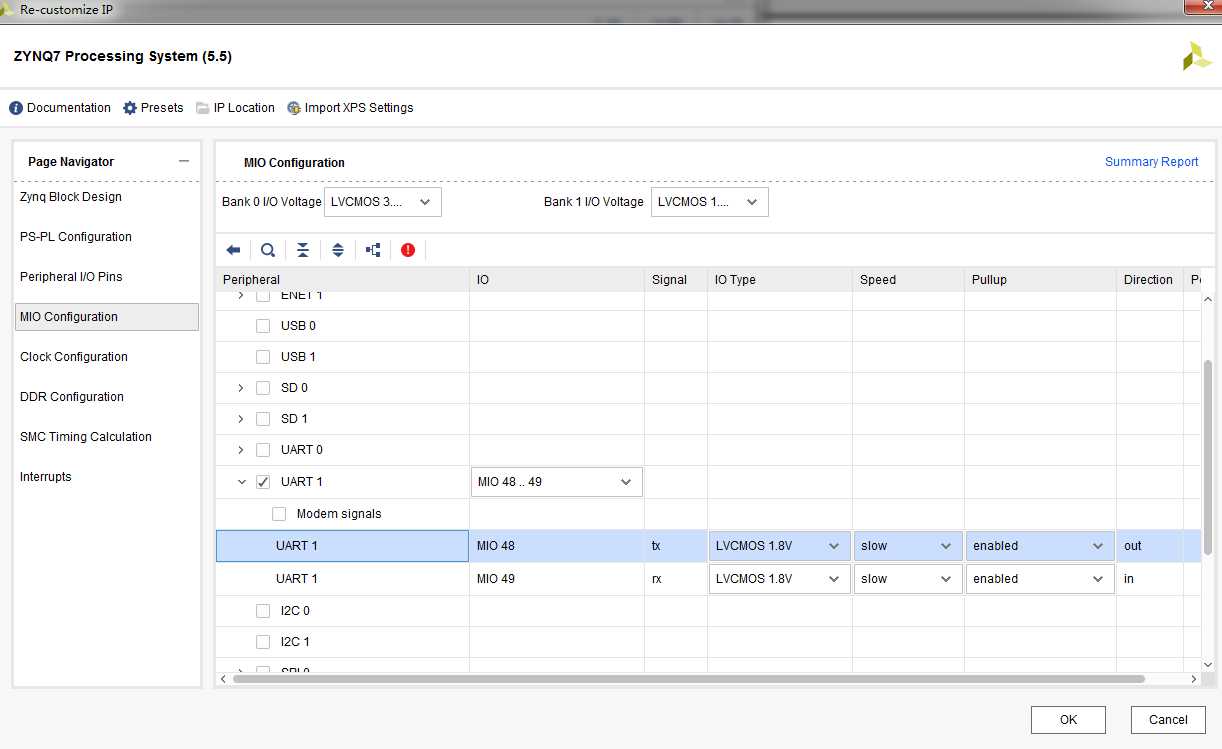

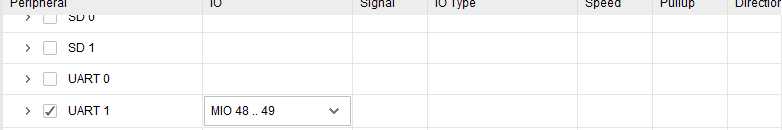

串口配置:

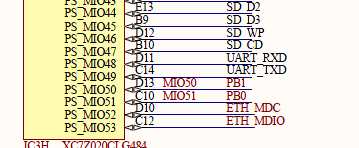

对照原理图看编译后的IO Port

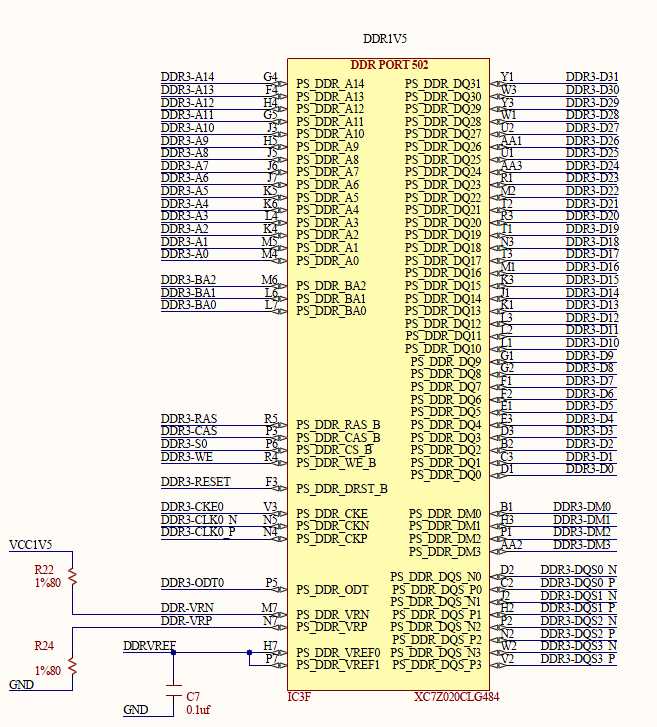

DDR端口的硬件电路与对应的引脚配置图:

因为我只使能了串口:

用的是48,49两个脚,所以:

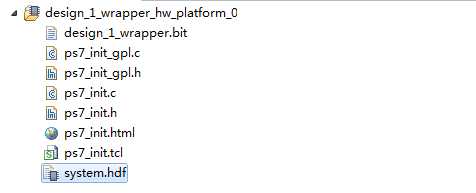

硬件信息:

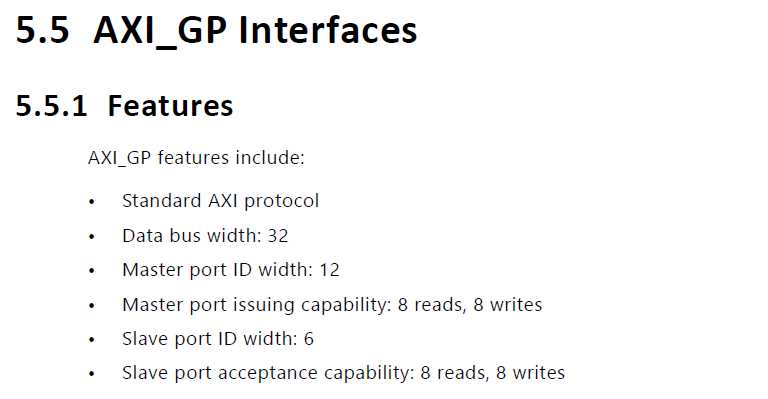

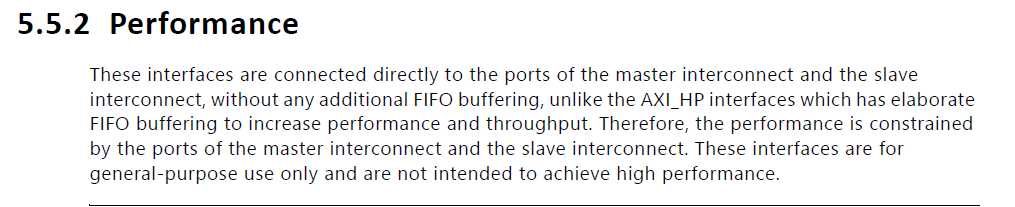

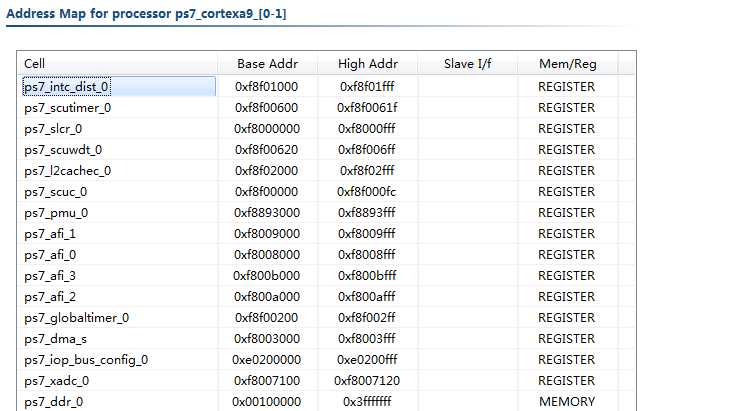

设备地址空间表:

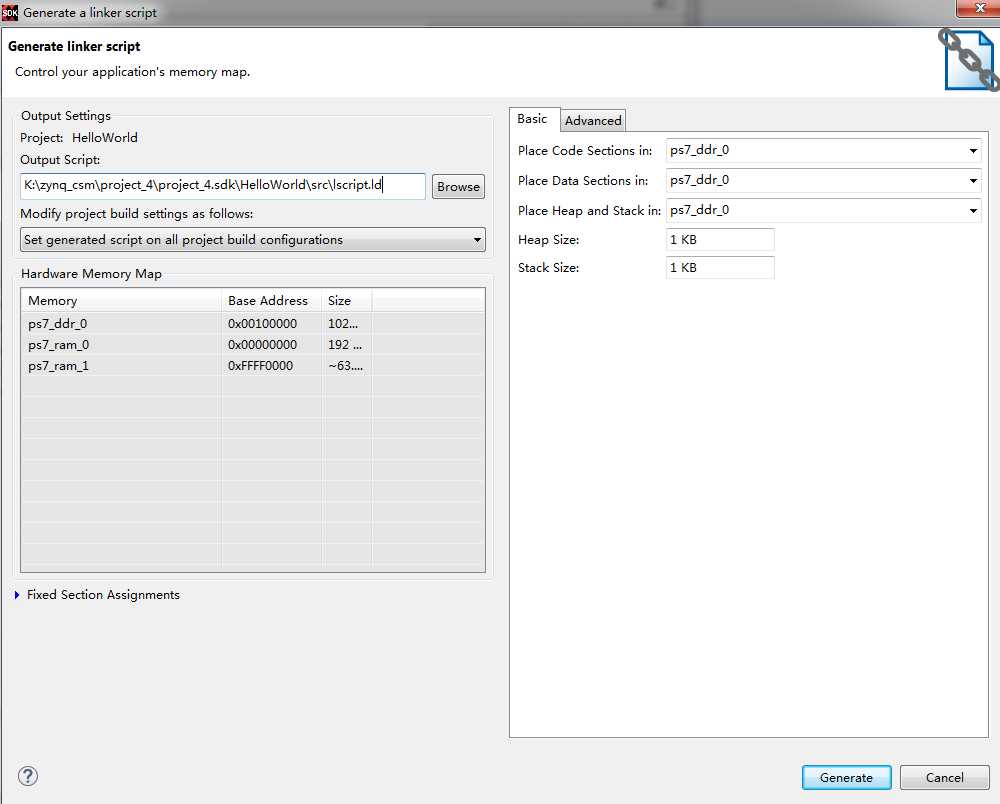

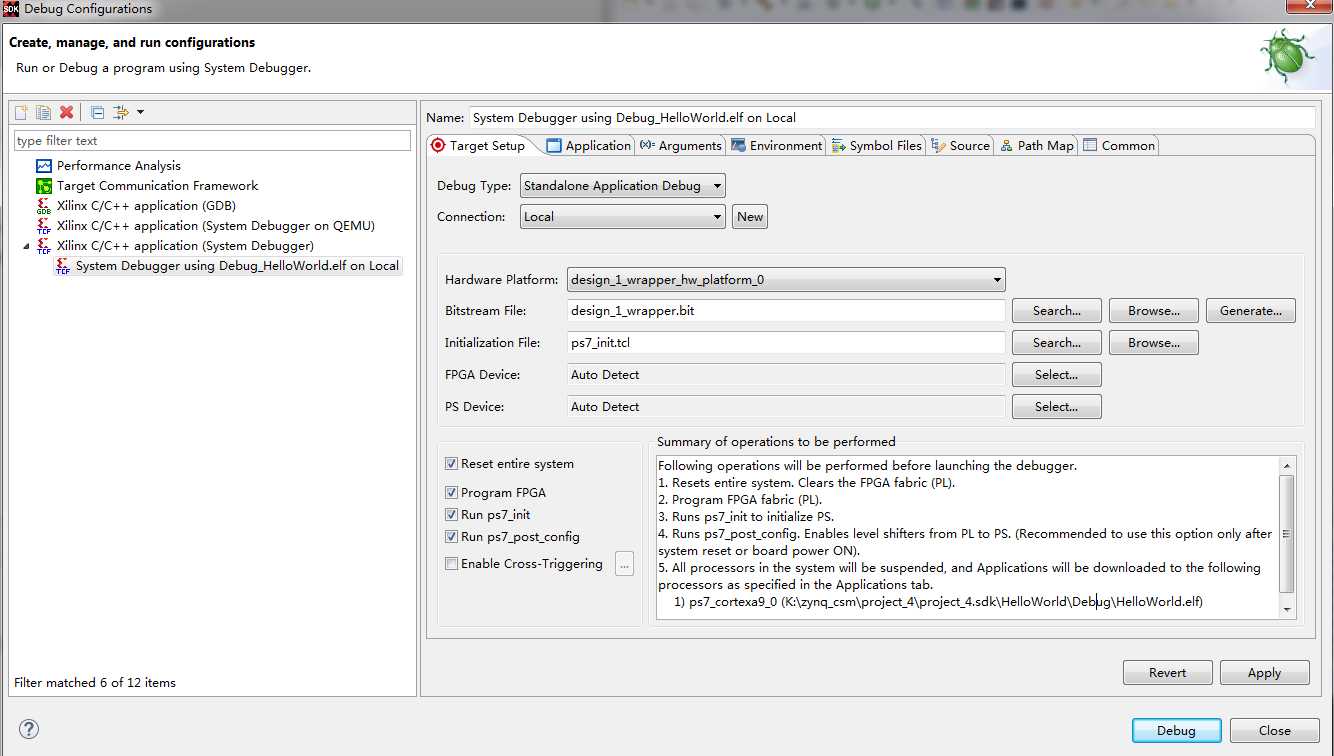

在SDK中有两个经常容易忽视的操作:

生成debug文件界面:

每次都复位整个系统,每次都对FPGA进行编程。

原文:https://www.cnblogs.com/chensimin1990/p/11601920.html