分频器的实质上就是一个计数器。

带复位功能的计数器:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity ripple is

port(

clk,rst:in bit;

cnt:out std_logic_vector(1 downto 0)

);

end ripple;

architecture bhv of ripple is

signal cnt0:std_logic_vector(1 downto 0);

begin

process(clk,rst)

begin

if rst=‘1‘ then

cnt0<=(others=>‘0‘);

elsif clk‘event and clk=‘1‘ then

cnt0<=cnt0+1;

end if;

end process;

cnt<=cnt0;

end bhv;

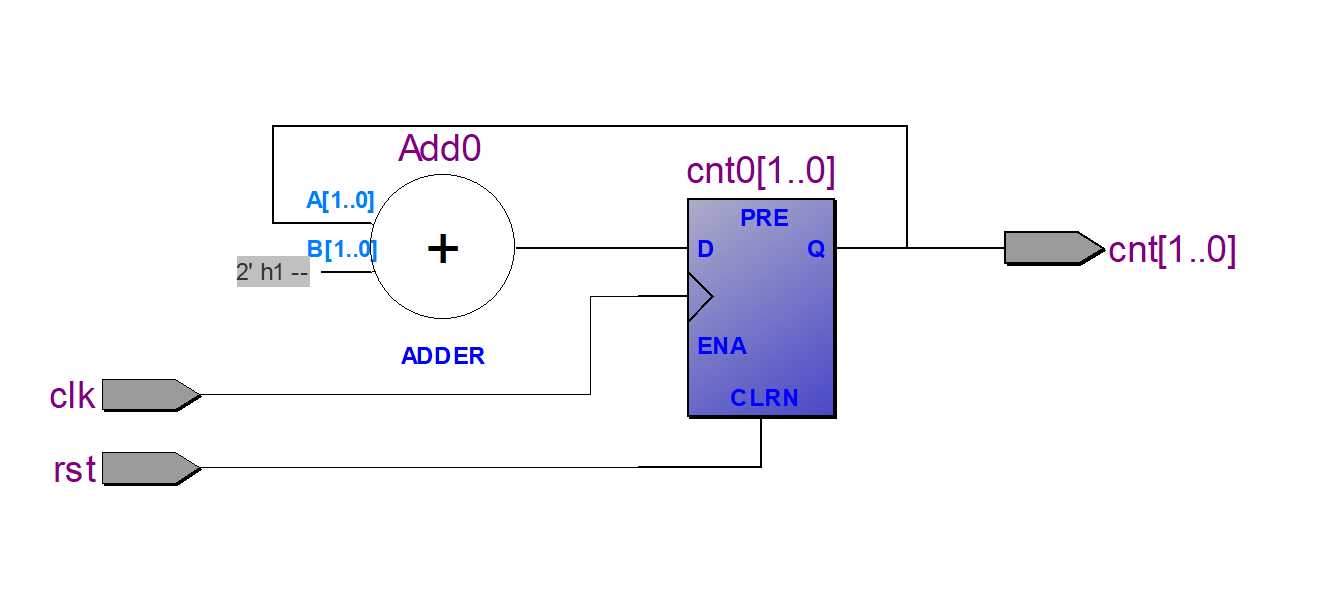

RTL原图:

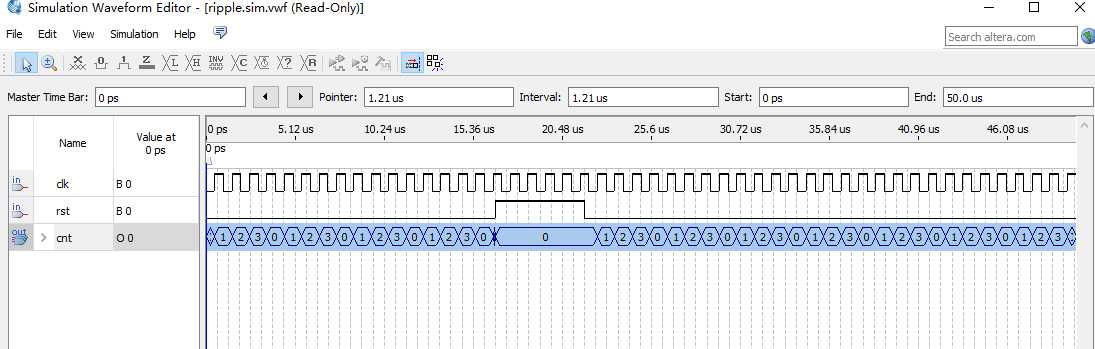

仿真图:

原文:https://www.cnblogs.com/lhkhhk/p/11958793.html