在微机系统中产生定时信号的方法有 软件定时 和 硬件定时

软件定时就是写延迟函数循环,优点:编程简单,缺点:一直占用CPU时间,没有充分利用

硬件定时是有两种不同器件

一种是不可编程器件,此方法电路简单,通过改变电路中的阻容值

第二种就是可编程器件,如8253/8254,通过预先设定控制方式,定时时间等完成定时

8253按照设定的定时/计数常数进行递减,若作为计数器,则由外部事件控制计数器递减;若为定时器,则由内部事件控制计数器递减。8254只是多了一个读回命令和状态字。

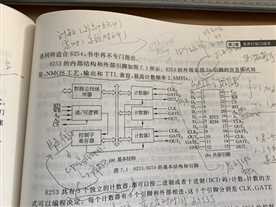

8253 内部结构

nmos 工艺,24引脚的双直插式封装(DIP),输出与TTL兼容,最高计数频率为2.6MHz

8253有3个独立的定时/计数器,可以按二进制/十进制(BCD码)计数,计数方式可编程。每个技术器有3个引脚和外部相连,分别是CLK,GATE和OUT

引脚图和功能图如下

数据总线缓冲期:它是8位3态,双向数据缓冲器,其功能是CPU向8253的控制寄存器写控制字;CPU向计数器012写入计数初值,如果是16位计数初值,需要写两次,先低八位后高八位(8253/8254与CPU连接的数据线却是8位的)

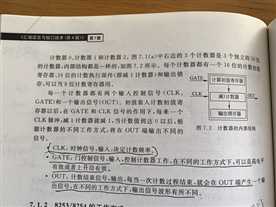

读/写逻辑电路:接收来自总线的5个控制信号,包括(RD)(WR),地址选择(A1A0)和片选信号(CS)

当CS=1的时候,片选未选中,后续所有操作都无效

当CS=0的时候,片选选中

看A1A0,00为0号计数器,01为1号计数器,10为2号计数器,11就是没有操作

看RD和WR,当RD为1,WR为0,写信号选通,开始向计数器设置初值

当RD为0,WR为1,读信号选通,开始读计数器计数值

下面是计数器的结构

可以看到

CLK是时钟信号,输入决定计数频率

GATE :门控信号,输入,控制计数器工作模式(上升沿有效/高电平有效)

OUT:计数结束信号,计数结束就会产生一个输出信号,输出波形随工作模式

设置完初值,在GATE和CLK信号下,来一个CLK信号,计数器-1

8253/8254工作方式

方式0:计数结束产生中断

方式1:可重复触发的单稳态脉冲

方式2:分频器

方式3:方波发生器

方式4:软件触发选通

方式5:硬件触发

8253有6种工作方式,每个通道均可以通过编程选择工作方式。

计数启动方式:

软件启动:GATE端为高电平,置入计数初值后的第2个CLK脉冲的

下降沿就开始计数

硬件启动:GATE端要求有一个上升沿跳变,对应CLK脉冲的下降

沿开始计数

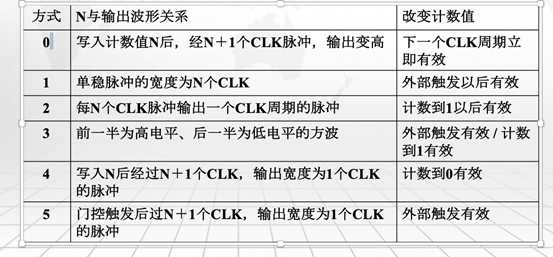

工作方式:

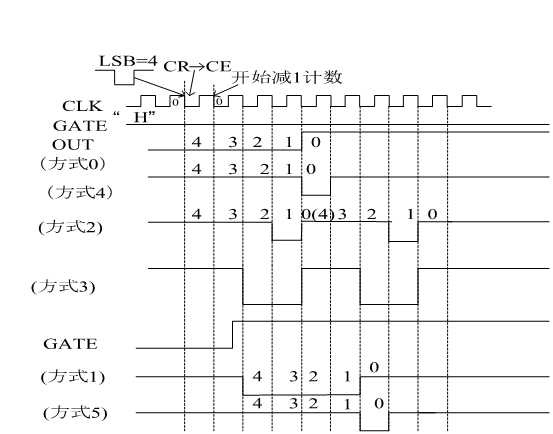

方式0:计数到零产生中断请求。软件启动。

方式1:硬件可重复触发的单稳态触发器。硬件启动。

(3)方式2:分频器。软、硬件启动。

(4)方式3:方波发生器(用得最多的方式)。软、硬件启动。

(5)方式4:软件触发选通。软件启动。

(6)方式5:硬件触发选通。硬件启动。

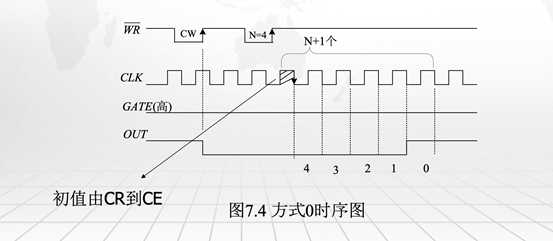

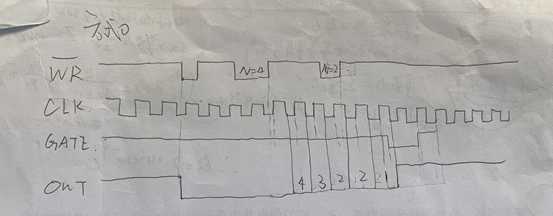

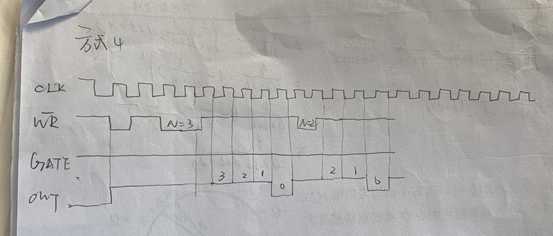

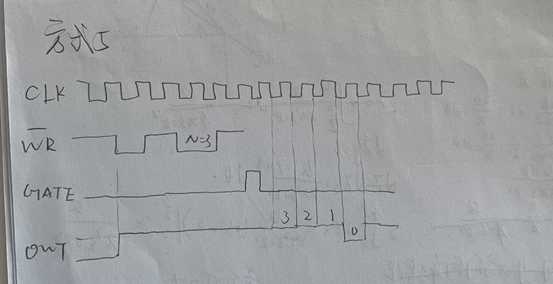

方式0:

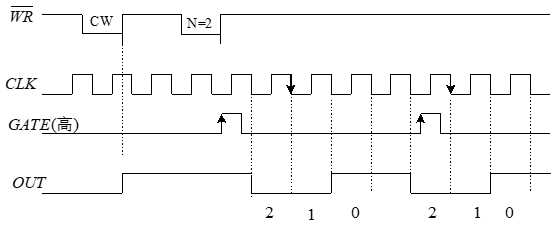

当WR发出选通信号的时候,OUT立刻为0,当CPU填入初值的时候,从下一时刻开始计数,计数到0的时候,OUT立刻为1(门控信号始终为1)

如果中间GATE信号为0,则中断计数中断,直到GATE信号为1的时候重新开始计数。

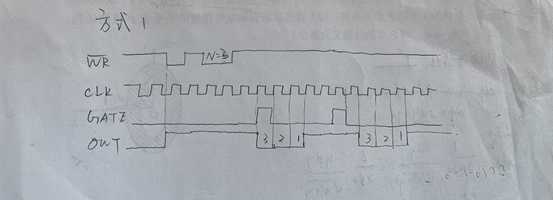

方式1:单稳态脉冲可重复触发

OUT初始为低电平,当WR选通的时候,OUT为高电平。此时等待GATE的上升沿。当GATE为高电平的时候

① 若设置初值为N,则输出为N个CLK周期宽度的负脉冲。

② 计数到零时,可再次由GATE上升沿触发,输出同样宽度的负脉冲,而不必重新写入初值,即可重复触发如图7.7所示。

③ 在计数过程中(输出负脉冲期间),可由GATE上升沿再触发,如图7.8所示。

④ 在计数过程中,CPU可改变初值,这时计数过程不受影响,计数到0后输出变高。当再次触发时,计数器才开始按新的计数初值计数。即改变计数初值是下次有效的。

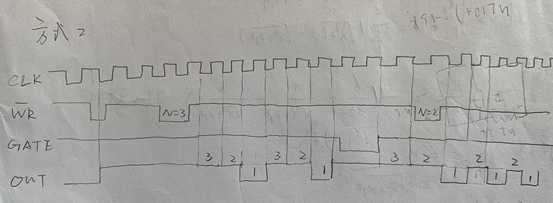

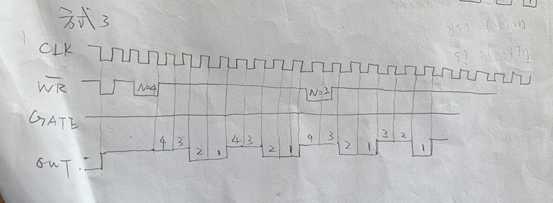

方式2 分频器

① 不用重新设置计数初值,通道能连续工作。如果初值为N,则每输入N个CLK脉冲,输出一个负脉冲,负脉冲的宽度为1个CLK周期,重复周期为N倍的CLK周期。

② 计数过程中可由GATE信号控制,当GATE信号变低时,立即暂停现行计数;当GATE信号变高后,从计数初值开始重新计数,如图7.9所示。

③ 如果在计数过程中,CPU重新写入计数初值,则对于正在进行的计数无影响,而是从下一个计数操作周期开始按新的计数值改变输出脉冲的频率,如图7.10。

方式3 方波产生器

① 注意初值N为偶数或奇数时,输出信号的差别。N为偶数时,输出对称方波,周期为N个CLK宽度;N为奇数时,输出有N+1/2个CLK周期的高电平和N-1/2个CLK周期的低电平。

② 在计数过程中,GATE信号变低则暂停现行计数过程,直到GATE变高,将从计数初值开始重新计数。

③ 如果要求改变输出方波的频率,则CPU可在任何时候重新写入初值,并从下一个计数操作周期开始改变输出方波频率

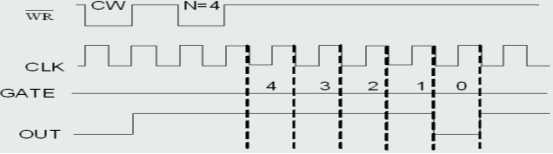

方式4:软件触发选通

① 若初值为N ,则写入初值后的N+1个CLK脉冲才输出一个负脉冲,负脉冲的宽度为一个CLK周期,如图7.12。

② 当GATE=1时,允许计数;GATE=0时,禁止计数。

③ 在计数过程中改变初值,则按新的初值重新计数,即改变初值是立即有效的。

方式5:硬件触发选通

① 初值为N,则在门控GATE上升沿触发后。经过N+1个CLK脉冲,才输出一个CLK周期的负脉冲,如图7.13。

② 若在计数过程中再次出现门控GATE触发信号。则将从初值开始重新计数,但OUT输出的高电平不受影响,如图7.14。

③ 若在计数过程中改变初值,只要在计数到0之前不出现新的门控触发信号,则原计数过程不受影响;等计数到0并出现新的门控触发信号后,再按新的计数初值计数。若在写入了新的计数初值后,在未计数到0之前有门控触发信号出现,则立即按新的计数初值重新开始计数。

总结,比较

⑴ 方式2(分频器)、方式4(软件触发选通)和方式5( 硬件触发选通),它们的输出波形相同,都是宽度为 1个CLK周期的负脉冲。区别是:方式2是自动重复工作的,而方式4需要由软件(设置计数初值)触发启动,方式5需要由硬件(门控GATE信号)触发启动。

⑵ 方式5(硬件触发选通)与方式1(硬件触发单稳),触发信号相同,但输出波形不同:方式1输出为宽度是N个CLK周期的负脉冲(计数过程中输出为低) ,而方式5输出为宽度是1个CLK周期的负脉冲(计数过程中输出为高)。

⑶ 6种工作方式中,只有方式0,写入控制字后输出为低;其余5种方式,都是写入控制字后输出为高。

⑷ 6种工作方式中的任何一种方式,只有在写入计数值后才能开始计数。方式0、2、3、4都是写入计数初值后,计数过程就开始了。而方式1和方式5在写入计数初值后,需由外部GATE信号的触发启动,才能开始计数过程。

⑸ 6种工作方式中,只有方式2(分频器)和方式3(方波发生器)为自动重复工作方式,其他4种方式都是一次 性计数,要继续工作需要重新启动。

图7.15是8253六种工作方式下的输出波形图。

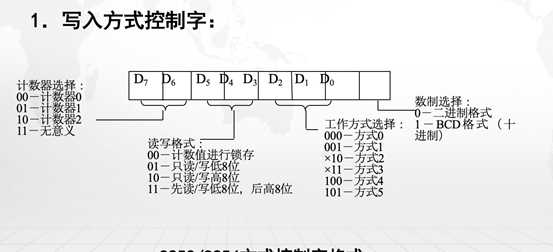

8253/8254的编程

因为8253没有复位,只能先写控制字初始化

8253中,D7D6为11为非法,8254中为读回命令

D5D6为读写格式,

如果写入的初值为0-255,选01

写入初值大于255,但低位全为0,选10

如果大于255,低位不为0,选11

如果想读出,选00,直接进行锁存

D0选择计数初值的格式,1为十进制,0为二进制

注意的问题

计数初值的计算有下面几种情况:

当计数器工作在方式2或者方式3的时候,实际上是一个分频器,因此计数常数就是分频系数,分频系数=ƒi/ƒo(ƒi:输入CLK频率;ƒo:OUT端输出频率)。

当计数器作为定时器工作时,CLK通常来自系统内部的时钟,计数常数就是定时系数,定时系数=T/tCLK=T׃CLK(T为定时时间,ƒCLK为输入的CLK频率)。

当计数器作为外部计数使用时,计数脉冲通常来自系统外部,计数常数就是要记录的外部事件的脉冲个数。

3 计数返回

8253想读当前计数值,先发命令字锁存,然后先读低八位,再读高八位

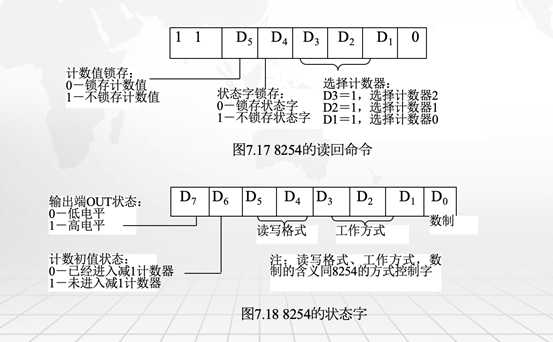

8254,可以将3个计数器的计数值和状态都锁存,向CPU返回命令字

8253的计数值的读回

由CPU访问每个通道的输出锁存器OL,即可实现读出每个通道的计数值。

在上面的方式控制字格式中,我们看到,如果D5D4=00,就表示锁存该计数器的值,用来进行读入。

8254的计数值和状态读回

多了专门的读回命令字,可以将3个计数器的计数值和状态都进行锁存,并且向CPU返回一个状态字

读回命令写入控制端口,而状态字和计数值都通过相应的计数器端口读出

原文:https://www.cnblogs.com/Kevin-Weng/p/11985964.html