1. 仿真事件队列

VCS仿真工具怎么处理交给他的代码,VCS支持Verilog、SV、VHDL、C语言

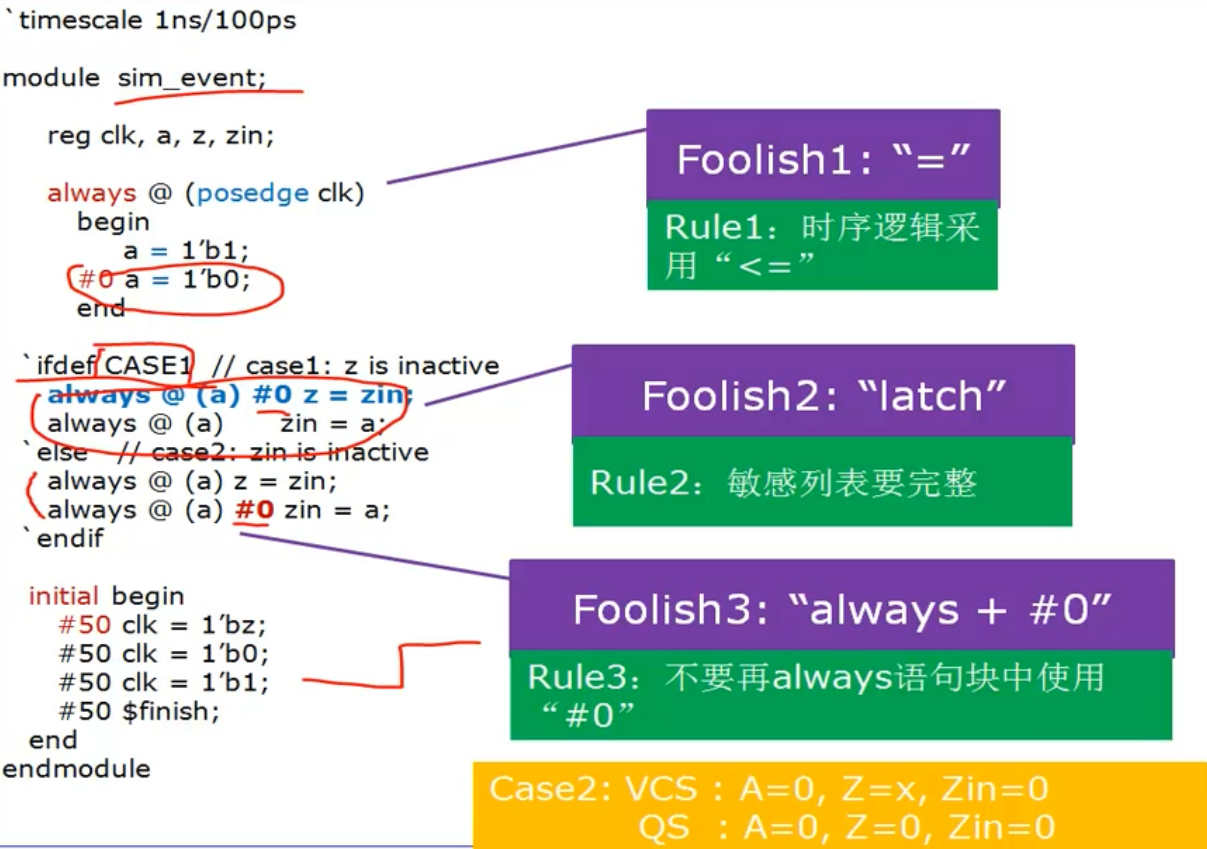

PPT1

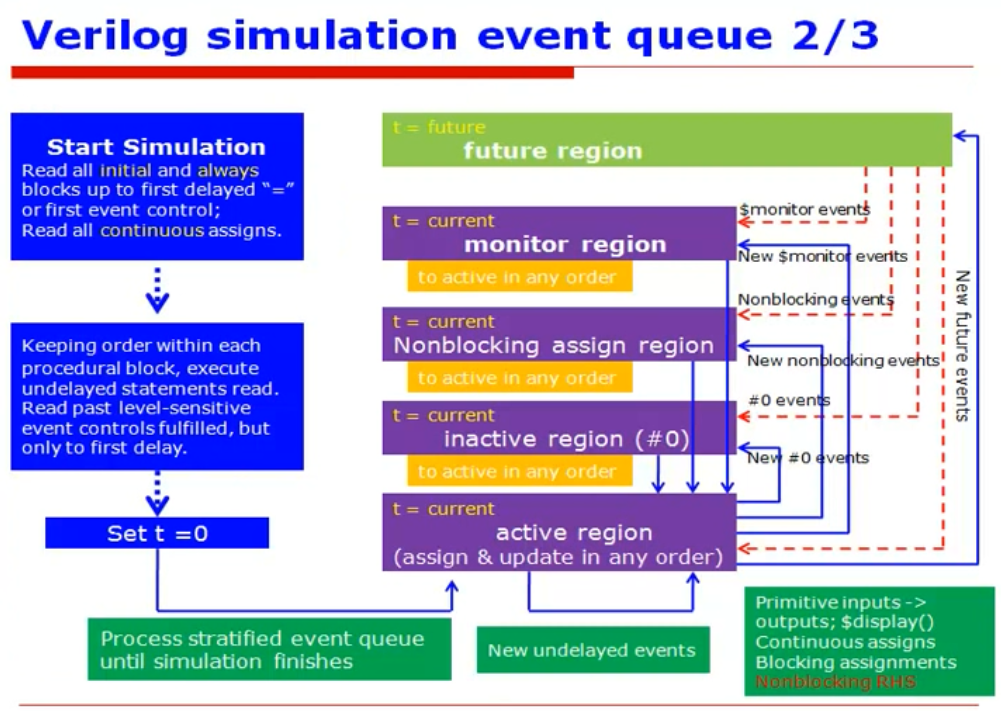

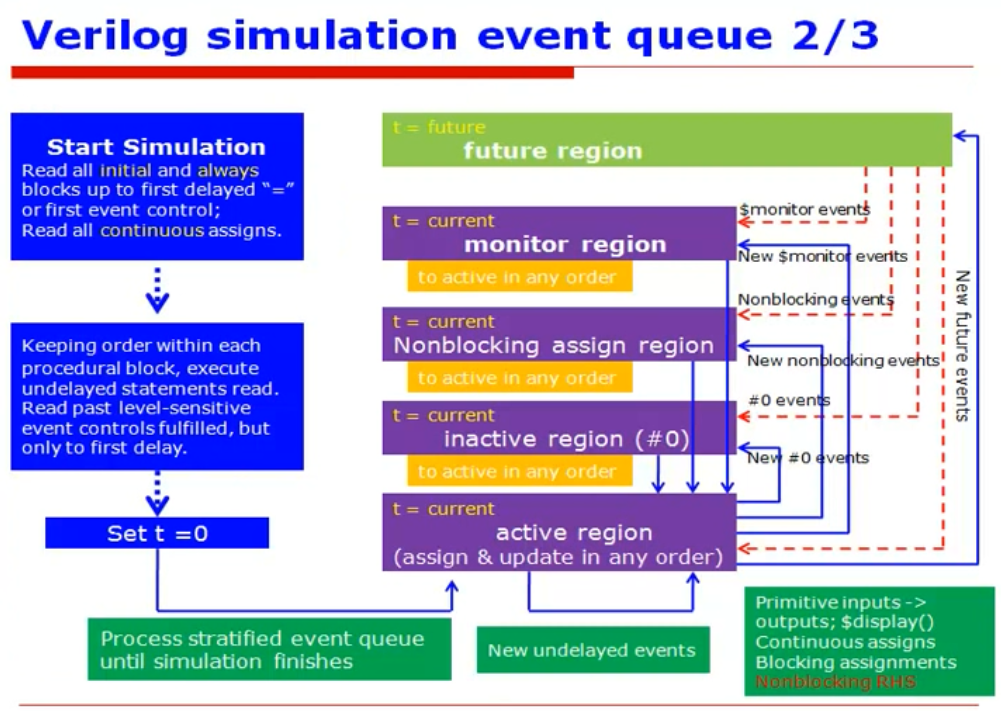

CPU的环境的基于指令的,硬件电路和软件的不同,并发执行。怎么通过软件模拟硬件的并发性

- IEEE1364: Verilog语言的仿真基于分层的事件队列

- 执行事件的队列

- 仿真时间的计算

- Verilog仿真器先从没有延迟的事件开始,执行他们,然后把时间设成0,然后按照时间循序一次执行各个事件

- Verilog语言规范没有规定当多个事件被安排在同一个时刻来 调度时,应该执行那个

- 只要在同一层的事件,什么执行循序都是可以的

- 设计师必须理解Verilog的分层次仿真事件队列

PPT2

- 首先执行没有延迟的语句(Iniital 语句)

- active区域:primitive input...特别的 是非阻塞赋值右边的计算

- inactive区域:

- Nonblocking区域

- monitor是赋值后的新值,display是旧值

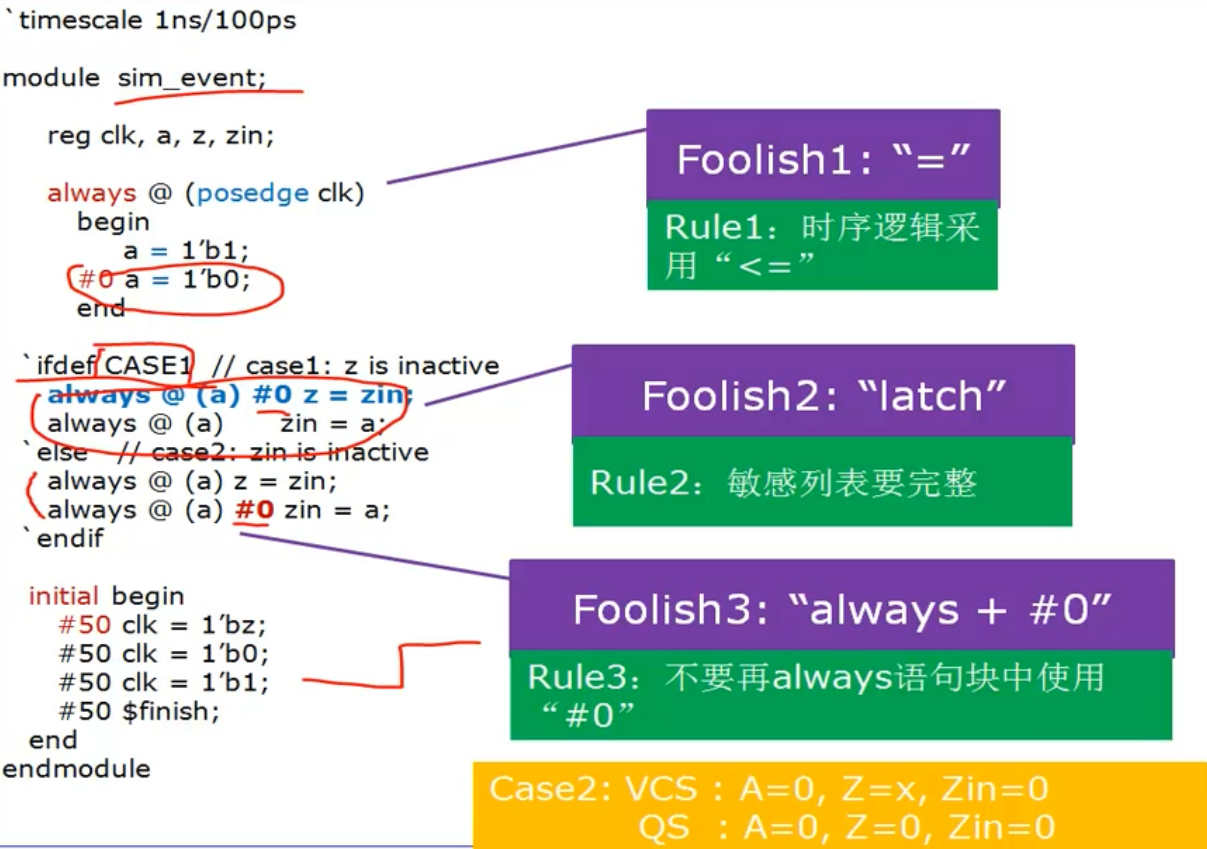

PPT3

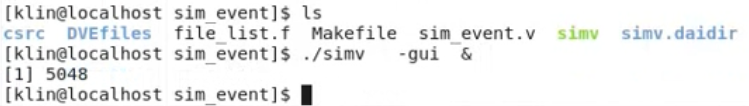

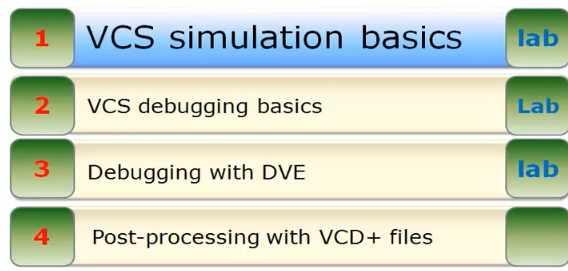

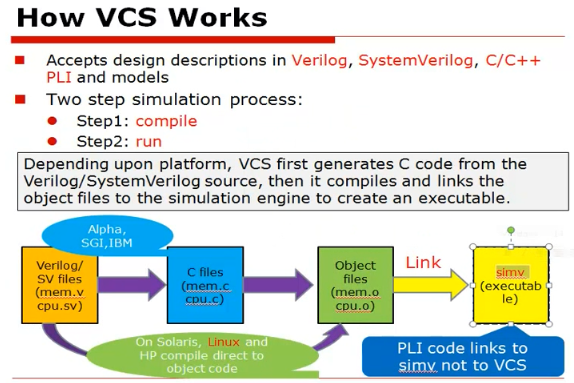

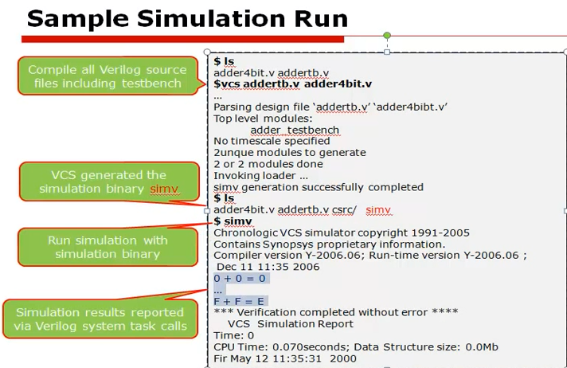

VCS对仿真文件进行编译

编译后,得到了simv的二进制可执行文件

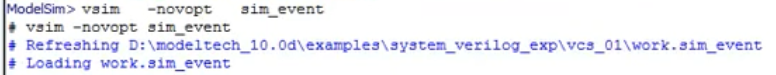

define CASE1VCS执行得到的结果为,时钟跳变沿:a = 0, z = 1, zin = 1

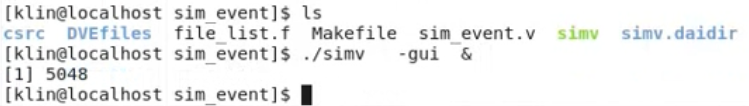

modelsim的编译后执行,得到的结果为: a = 0, z = 0, zin = 0

对于仿真这一段代码来说,没有正确之分

2. 课程介绍

PPT1

vcs在企业级的数字逻辑仿真里面用的十分的多

Prerequisites

You should have experience in the following areas:

- Understanding of digital IC design

- Familiarity with a Linux or Unix OS

- Familiarity with a Linux-based text editor (VI)

PPT2

Measurable Objectives

■ By the end of this workshop you should be able to:

- Simulate Verilog/SystemVerilog designs using VCS

- Debug VeriIpg/SystemVerilog designs using VCS

- Run fast RTL-Level regression tests for your design

- Run fasti Gate-Level regression tests for your design(回归测试: 在新版本上运行所有已通过的测试用例以验证有没有“退化”情况发生,这个过程就是一个“Regression Test”。 )

- Acquire the skills and knowledge to successfully implement coverage driven verification methodology using VCS

代码覆盖率, 功能覆盖率

PPT3

Agenda

3. VCS介绍

PPT1

? A compiled simulator

- Verilog Compiled Simulator

- Digital functional simulator

- Complies with IEEE-1364

- Including PLI 1.0/VPI (PLI2.0) (Programming Language Interface)

- Supports simulation at multiple abstraction level(门级, RTL级)

PPT2

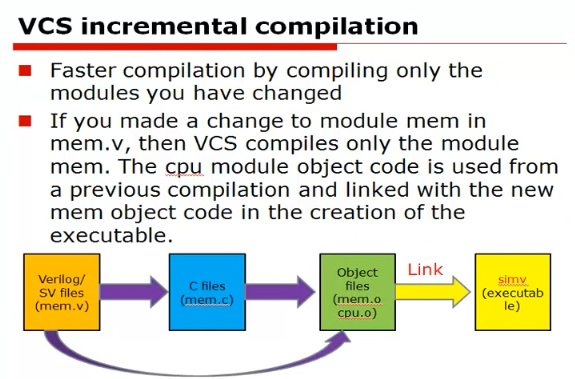

编译后的文件称为目标文件(object files)

4. 编译时的开关

PPT1 基本的编译

VCS Compilation Command Format

$ vcs source_files[compile_time_options]

- All Verilog/SystemVerilog source files of the DUT

- Separated multiple source files by spaces

- Top module should contain testbench for the DUT(顶层文件包括DUT, Design Unit Test)

Control how VCS compiles the source files (如何去编译)

Critical for optimization for visibility and performace (可视化,编译的性能)

Each unit of this workshop will describe how best to use these compile time options ()

- Generates simulation binary executable simv (binary executable file)

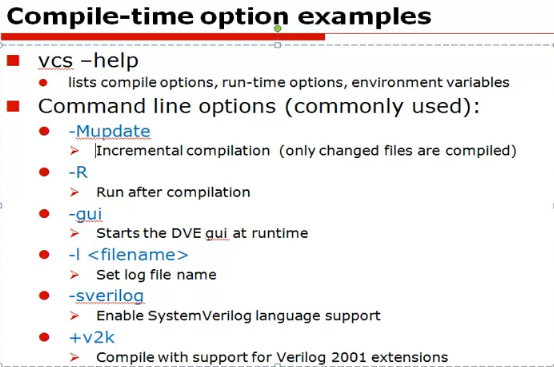

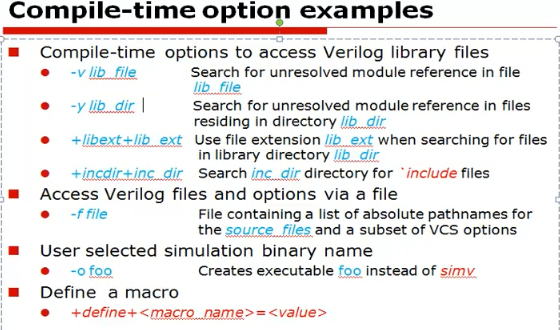

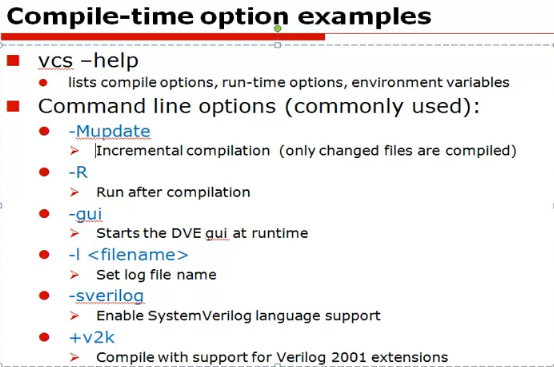

PPT2 编译选项1

增量编译, 编译后执行,打开GUI,将编译过程记录到文件,支持SV,支持verilog 2001的扩展

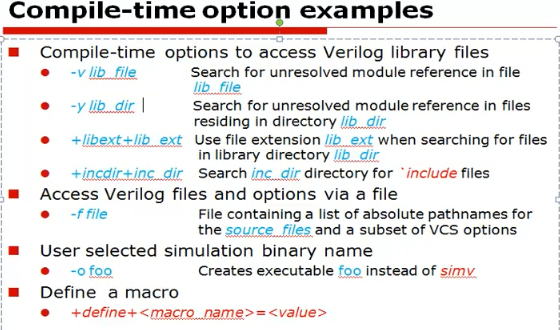

PPT3 编译选项2

编译使用了库文件,编译的文件在文件夹,编译用到了宏

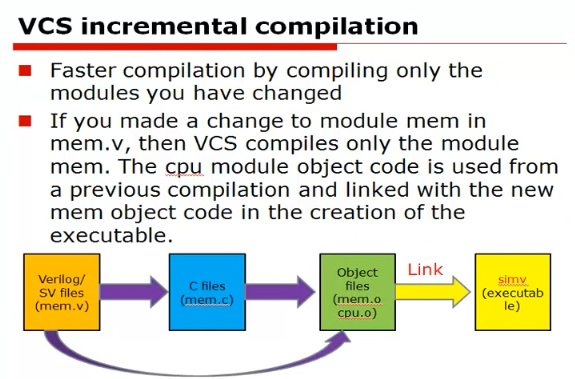

PPT4 增量编译

cpu.o并没有重新编译

5. 仿真时的开关

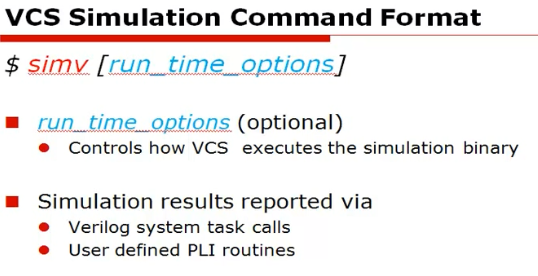

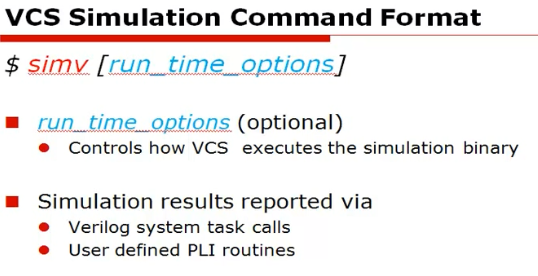

PPT1 基本的仿真

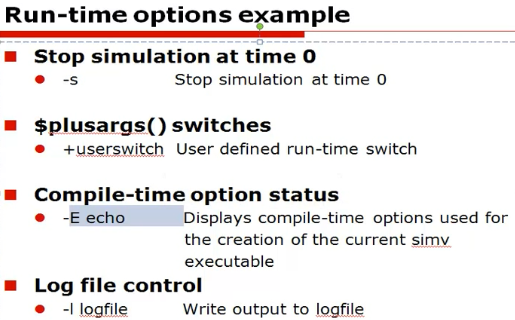

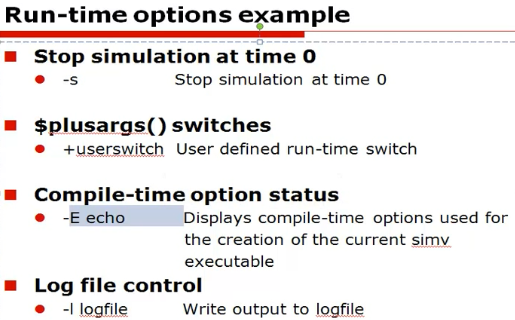

PPT2 仿真的开关选项

6. 例子说明

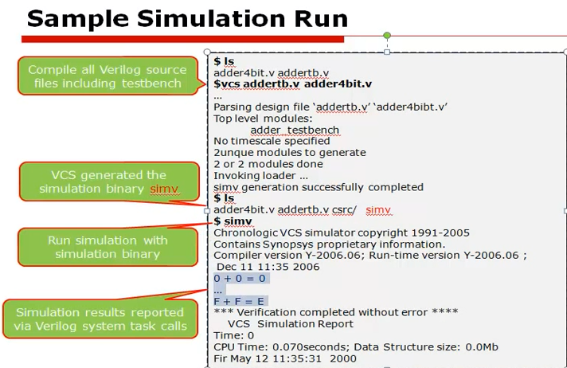

PPT1 实例

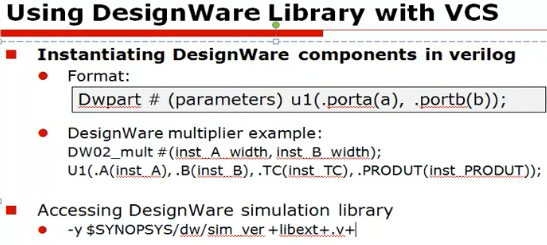

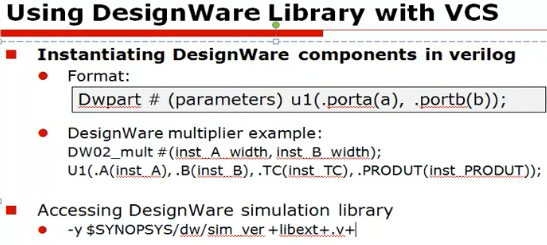

PPT2 使用了DW的库

7. 上机演示

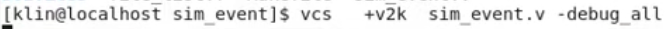

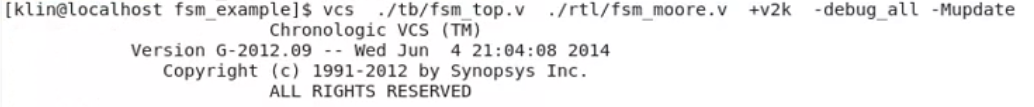

- 编译

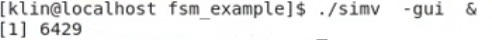

- 打开仿真

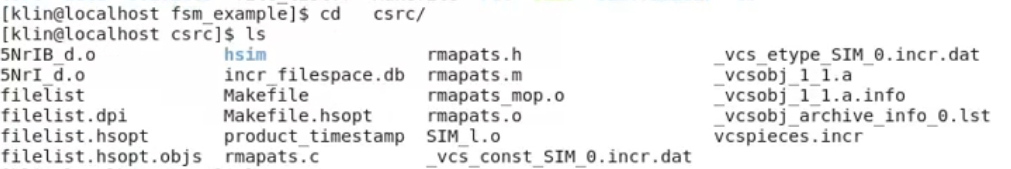

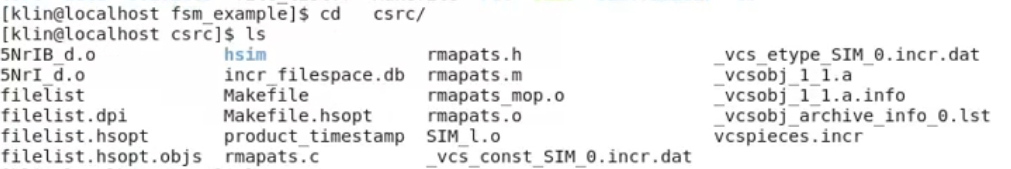

- 查看编译产生的内容

编译的结果包括了Makefile,用来增量编译的维护

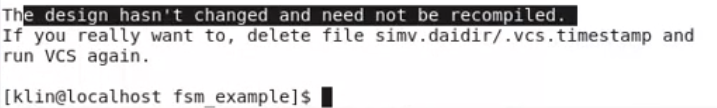

- 增量编译 Mupdate

增量编译没有任何改变,也就没有提示

- 编译的日志记录

有错可能是在那一行附近

- 编译之后立即仿真

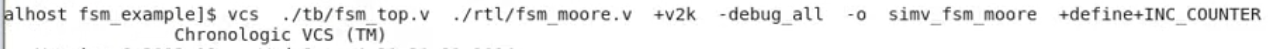

更改编译的文件的名称 -O

- 定义宏的方式

- 在文件头中添加`define INC_COUNTER (control + p vi自动补齐)

- touch global_define.vh 生成一个文件,保存宏定义, include “global_define.vh”,增加文件查找,如下图

- 通过开关定义宏

VCS课时1:仿真事件队列

原文:https://www.cnblogs.com/ICworkman/p/12063725.html