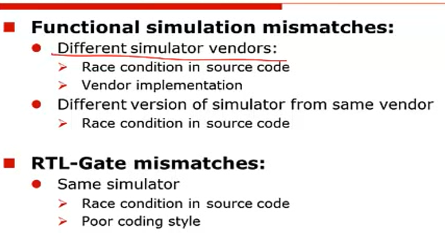

仿真的结果和预计的的不一样(debugging simulation mismatches)

if (data=3) //这个语句用于为真

好的coding方式

if(3===data)

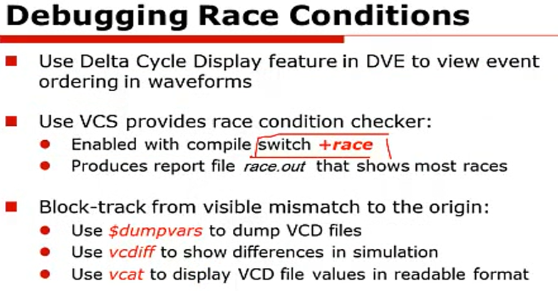

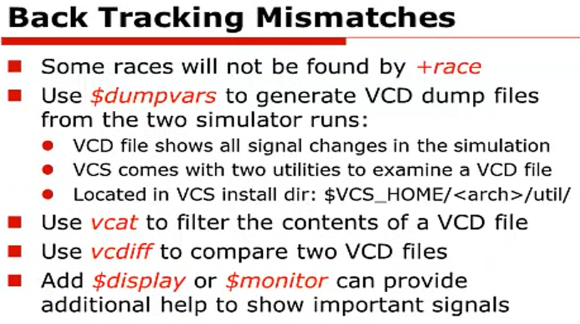

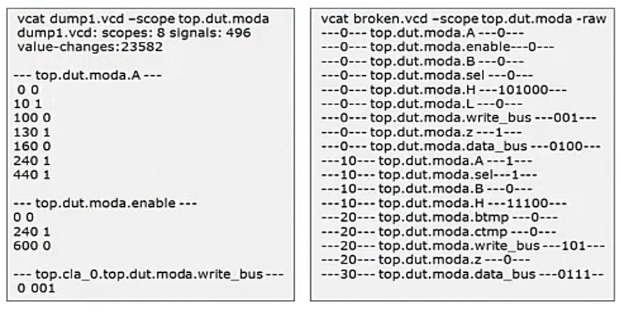

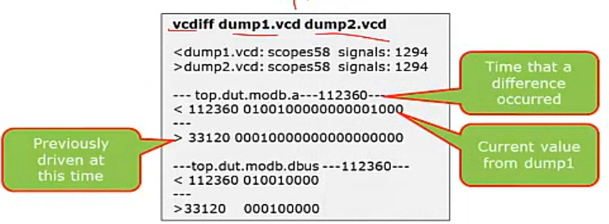

vcddiff比较vcd文件是不是一样

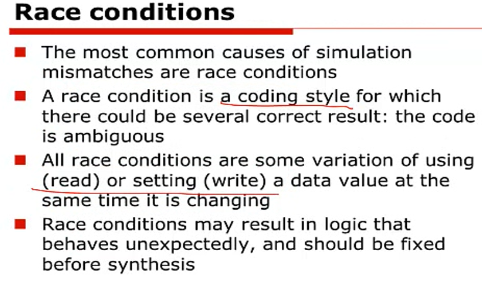

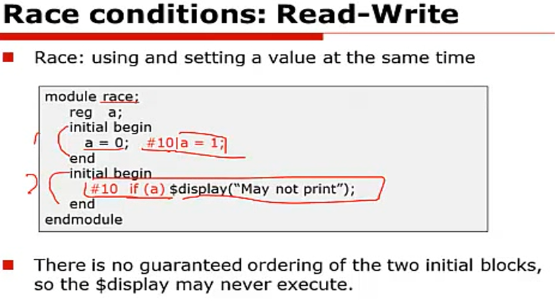

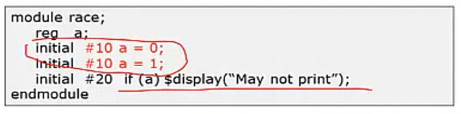

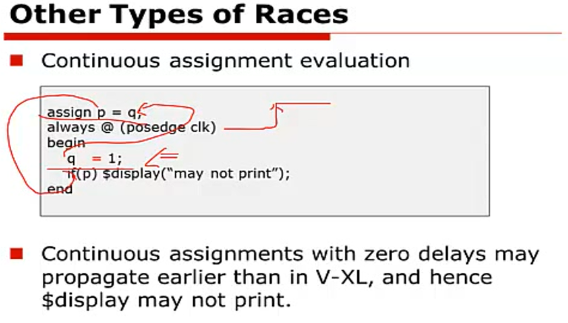

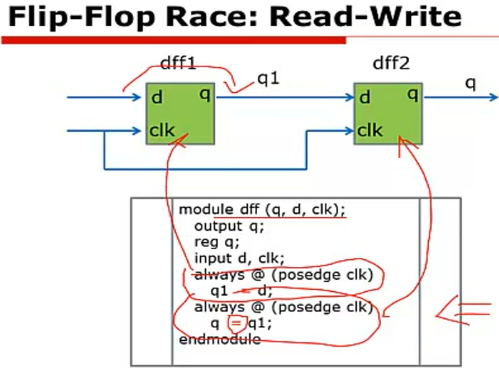

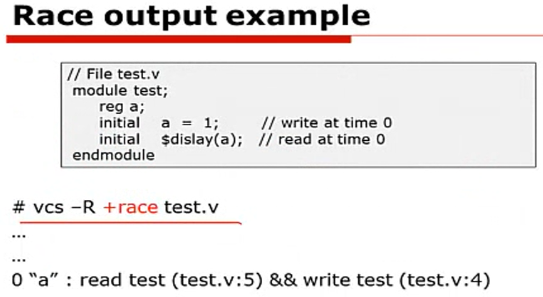

第10个仿真时间单位同时对a读取和写

在数字电路中避免这种coding style

不定态指的是,仿真的时候,复位信号到来之前未知的状态,真实的情况是不存在的

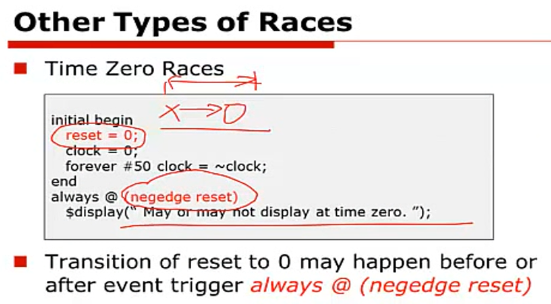

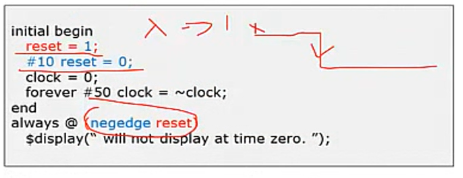

最开始的时候不知道reset=x是多少,如果最开始是不知道是什么

改进后为

#### PPT2

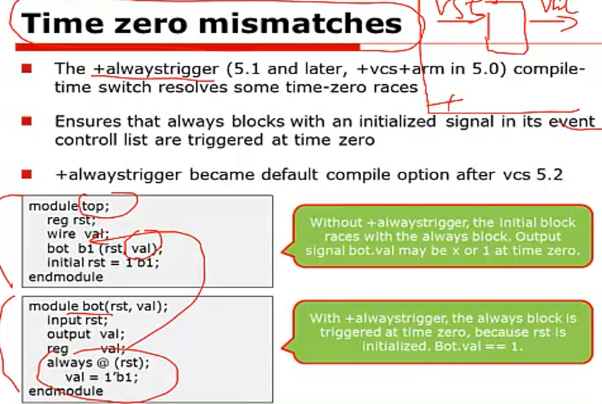

最开始的时候rst给1,那么val是多少呢

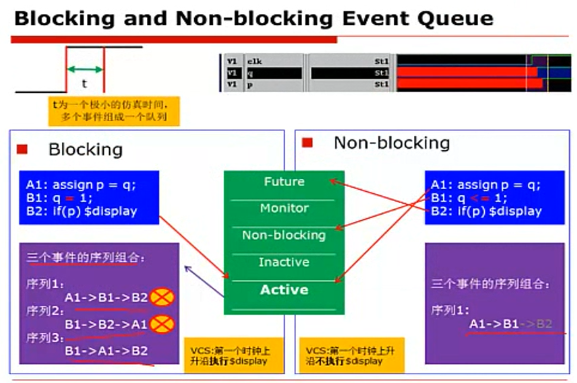

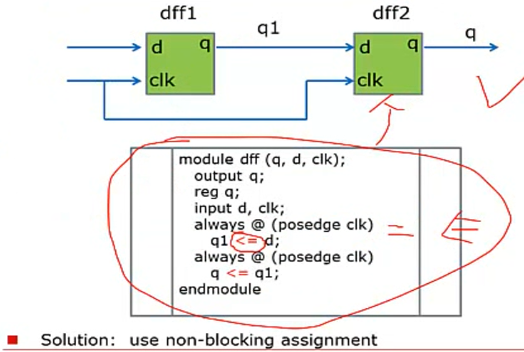

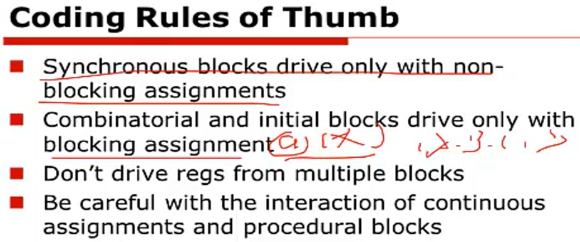

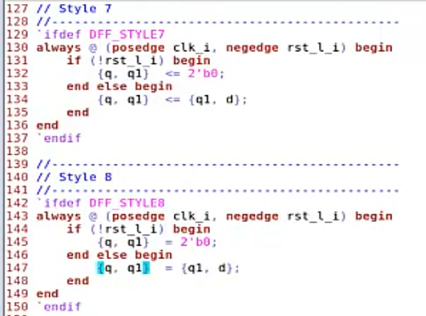

使用非阻塞电路的结构

多驱动,一般是在SoC顶层,双向端口

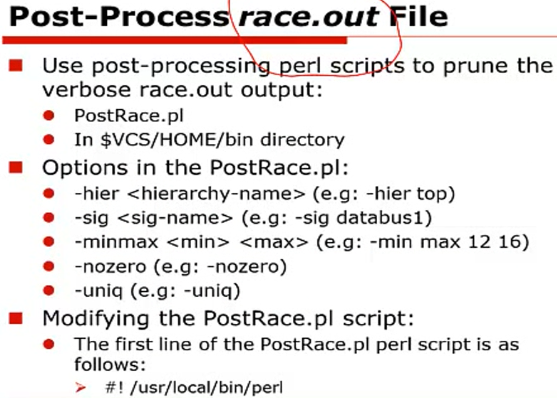

编译时加上开关选项

更多的是依靠人的经验的,少了一个等于号,通过方法避免

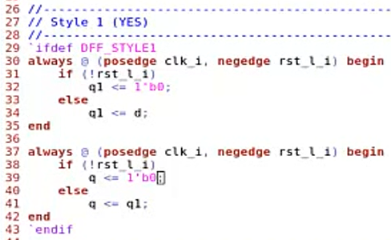

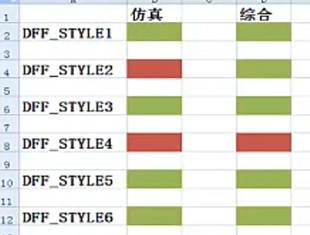

Style1 是非阻塞赋值

Style2 是阻塞赋值

结果并不是晚一拍

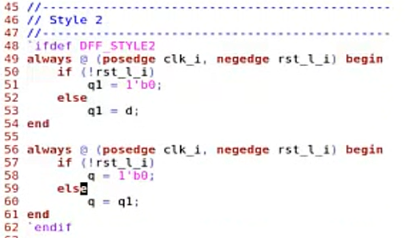

定义宏的方式:

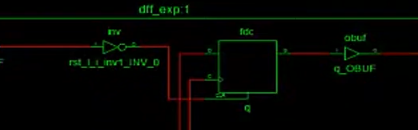

综合电路 `define DFF_STYLE2

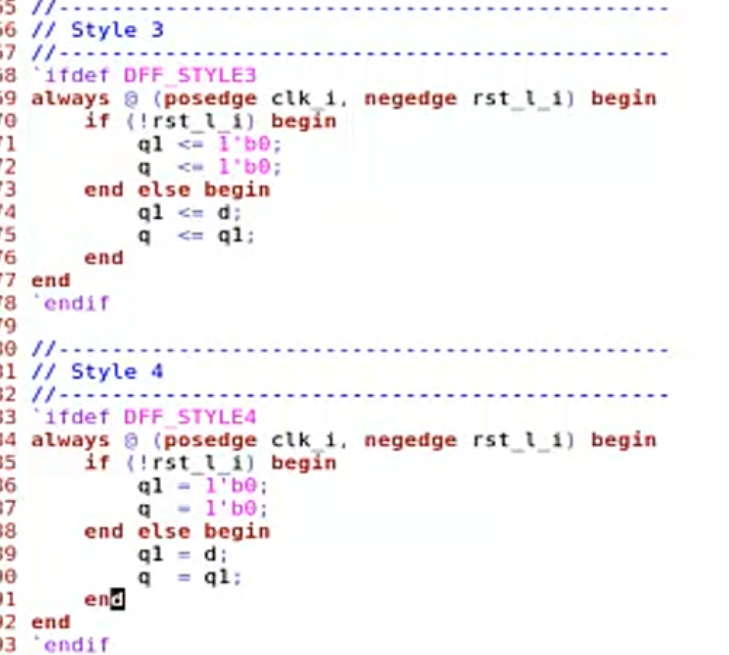

综合结果,第一种非阻塞结果是两个触发器,第二种是也是两个触发器

结论:综合结果是对的,仿真是错的

两级的触发器

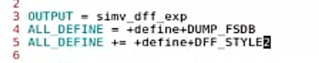

style3是两级的延迟,style4不是,是同一拍的,

Style4结果是只有1个触发器:

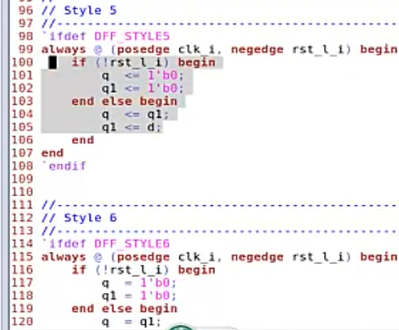

增加了第5种和第六种

顺序颠倒了

第五种仿真的结果是对的

第六种电路仿真结果是对的!

综合结果也是两个触发器

结论:通过阻塞赋值,有些情况仿真通过,但是综合不通过;有些仿真不通过,综合通过

原文:https://www.cnblogs.com/ICworkman/p/12079145.html