感谢syx,zkk,tn大佬的帮助,侥幸复习完毕

运算器、控制器

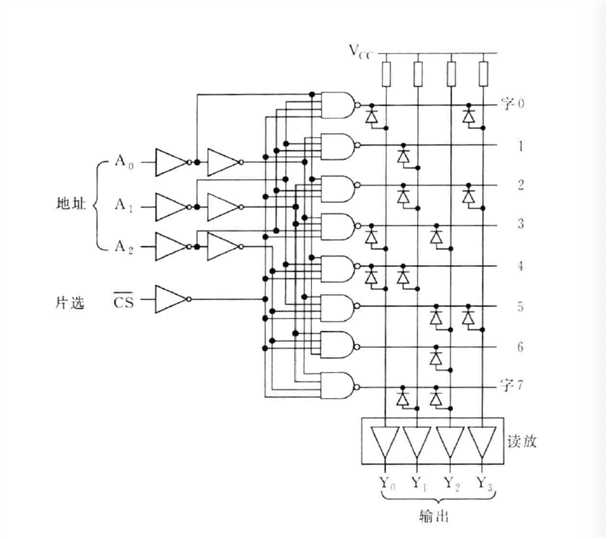

ROM 只读存储器

RAM 随机存取存储器

内存

内存单元序号

运算器、控制器、输入输出设备、总线、存储器、IO接口

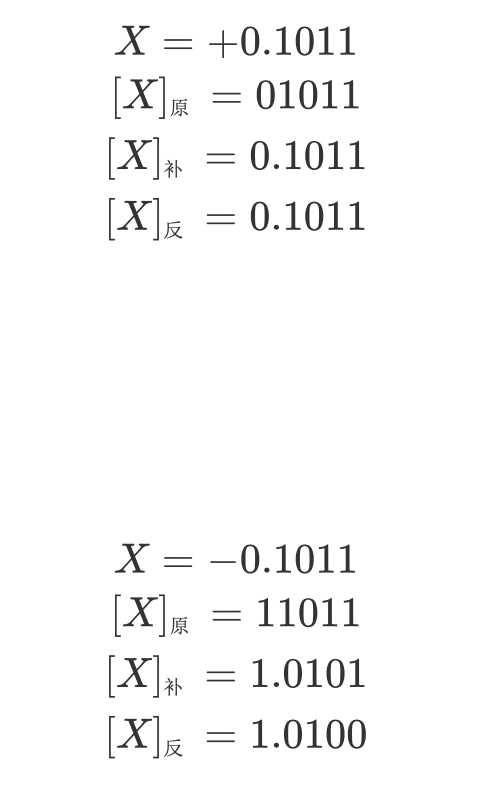

第一位为符号位置,0为正,1为负,符号参与运算

CPU运算1次能处理的最大位数

性价比:微型机,小型机,中型机,大型机,巨型机

计算机字长:8,16,32,64位

风格:微程序控制计算机,硬布线控制计算机

简单程度:精简指令系统计算机(RISC),复杂指令系统计算机(CISC)

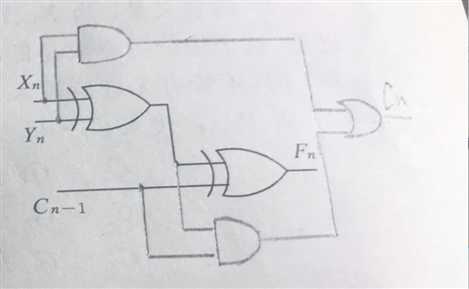

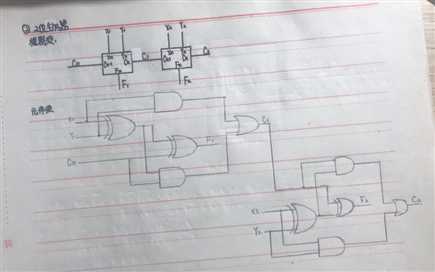

时序逻辑电路,组合逻辑电路,阵列逻辑电路

$$

N=MR^E\

浮点=尾数底^{阶码}

$$

酷睿i3,i5,i7,i9

操作码,地址码,寻址方式

x86:20根数据总线,16根地址总线

X88:32根数据总线,32根地址总线

工作原理:地址译码器根据输入地址选择某条输出(字线),再由它驱动该位线,以便读出字线上各单元存储的代码

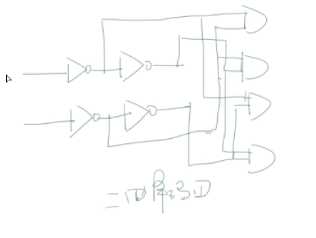

2-4译码器口诀:13 24 12 34

3-8译码器口诀 1357 2468 1256 3478 1234 5678

不同长度的数据存放在内存中的地址,必须是该类数据对应宽度的整数倍

通过对地址码的集中可能去排列组合,去除不可能的情况,对他们进行编号,使用n位二进制数去标识他们。

数字精度:一个数的有效位数

数据范围:计算机所能表示的一个数的最大值和最小值之间的范围

加电->初始状态下 自检->启动bios->bios引导操作系统->操作系统启动出现桌面

完整硬平台

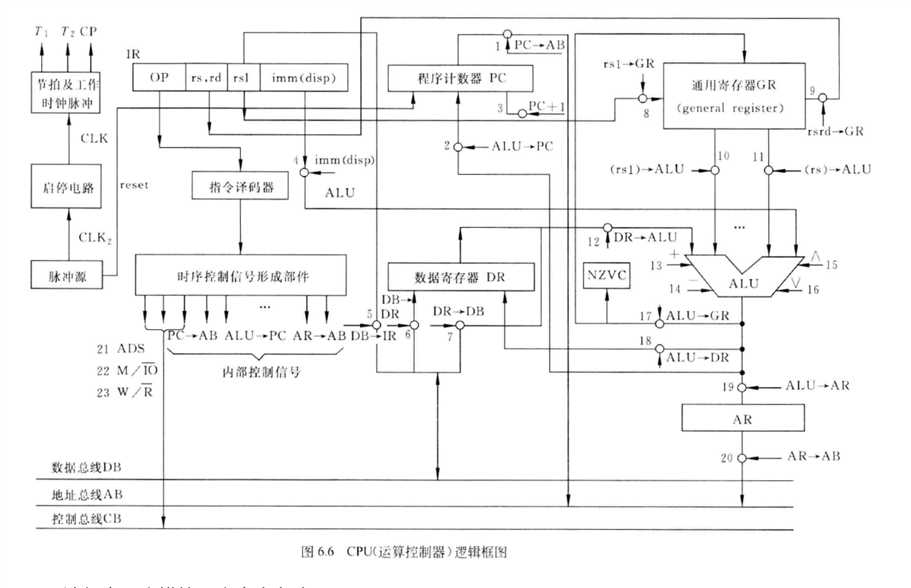

1)、任选一个模块写出中文名称

ALU:算数逻辑单元

PC:程序计数器

GR:通用寄存器

IR:指令寄存器

DR:数据寄存器

AR:地址寄存器

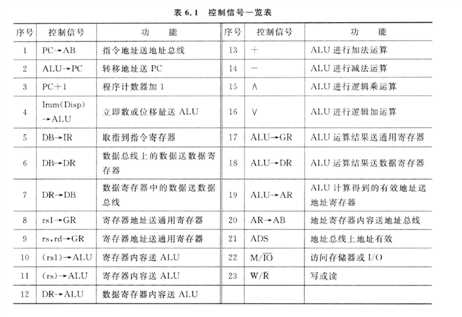

2)、选择一个或者三个控制信号,写出中文名称(哪个到哪个模块)?

3)、ALU的功能

完成加减法算数运算及逻辑运算

4)(主要)

A、给出一条指令,描述功能 (1‘)

MOV A,B 将寄存器B中的数移动到A

PUSH xx 将xx进栈

ADD A,B 将A和B相加,结果放在A

B、指令在硬平台不能运行,在图6.6改图,进行硬件升级(1’)

加2条,rs2->gr,(rs2)->alu

C、指令的分步执行(8‘)

1)取指令操作

PC->AB

ADS,M/IO=1,WR=0 打开访问控制权限,从存储器取指令送数据总线

DB->IR

PC+1

2) 计算微指令

Rs1->GR (rs1)->ALU disp->ALU

ALU->AR

3) 取数微指令

AR->AB

ADS,M/IO,W/R

DB->AR

4) 加法运算和送结果微指令

两个源操作数送ALU:rs->GR,(rs)->ALU,DR->ALU

ALU->GR

D、列出新的控制信号表(8’)

24 rs2->GR 寄存器rs2送到GR

25 (rs2)->ALU 寄存器rs2送到ALU

原文:https://www.cnblogs.com/littlepage/p/12122564.html