参考:https://blog.csdn.net/CrazyUncle/article/details/86164830

前言

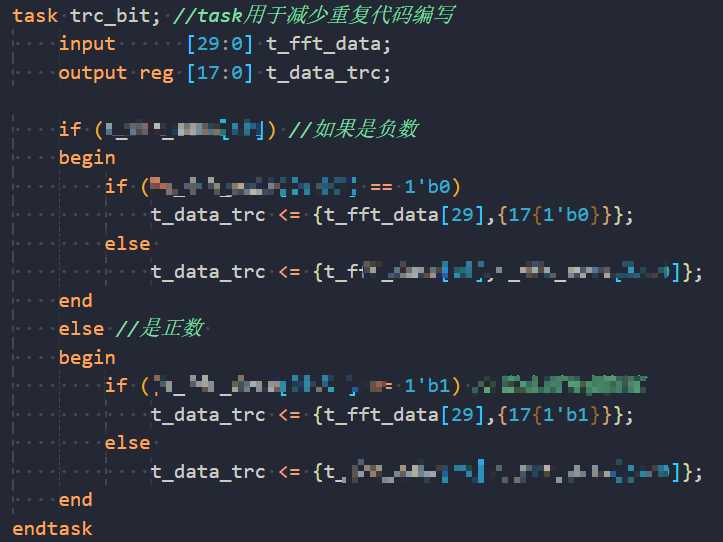

在进行多通道数据处理的时候,对于数据截位这样的操作,重复性的功能任务则可使用task进行预先定义,直接调用。

减少代码量及代码出错概率及后期修改容易程度。

流程

(1)任务的语法格式:

task <任务名>; <端口及数据类型声明语句> <语句1> <语句2> ... <语句n> endtask

(2)任务注意事项:

第一行task语句中不能列端口名称,system verilog中可以。

输入输出端口数量不受限制,但输出只能为reg。

任务中不能出现initial,always。但任务可在initial、always中使用。

vivado支持task综合,但需保证task中的代码本来就是可以综合的。

(3)实际代码验证:

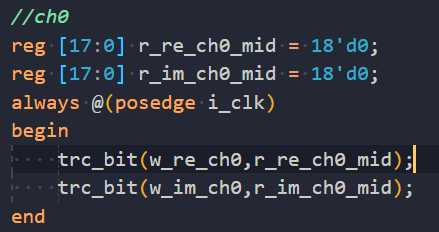

调用此task:注意输入输出要一一对应。

vivado已经验证,是可以综合的。

以上。

原文:https://www.cnblogs.com/kingstacker/p/12195895.html