13 DMA(Direct memory access)

13.1 DMA介绍

DMA(直接存储器存取)是用来给外设与存储器以及存储器与存储器提供高速的数据传输。

数据可以通过DMA快速地移动而不需经过CPU。

这使得CPU资源可以用于其他操作。

两个DMA控制器一共有12个通道(DAM1有7个,DAM2有5个),

每一个都能专注地管理一个或多个外设的存储器访问请求。

有一个仲裁机制处理DMA请求的优先级问题。

13.2 DMA主要特性

12个可配置的独立通道:DMA1有7个,DMA2有5个。

12个通道都连接到专用的硬件DMA请求,

每个通道也支持软件触发。这由软件进行配置。

DMA通道的请求优先级是可以通过软件编程设置的,

优先级等级包括:非常高、高、中、低,

如果是同等级的话,请求1有限请求2。

独立的源点和目标点传输大小,模拟打包和拆包。

源点和目标点地址必须与数据大小对齐。

支持循环缓冲区管理。

有3个事件标志:DMA传输一半、DMA传输完成以及DMA传输错误。

每个通道的单独中断请求对于这三个事件标志会逻辑上或在一起。

存储器与存储器之间的传输。

外设到存储器、存储器到外设、外设到外设都是可以传输的。

FLSH,SRAM,挂在APB1、APB2与AHB上的外设都可以作为DMA传输的源点和目标点。

传输的数据量是可以设置的,最高可达65536。

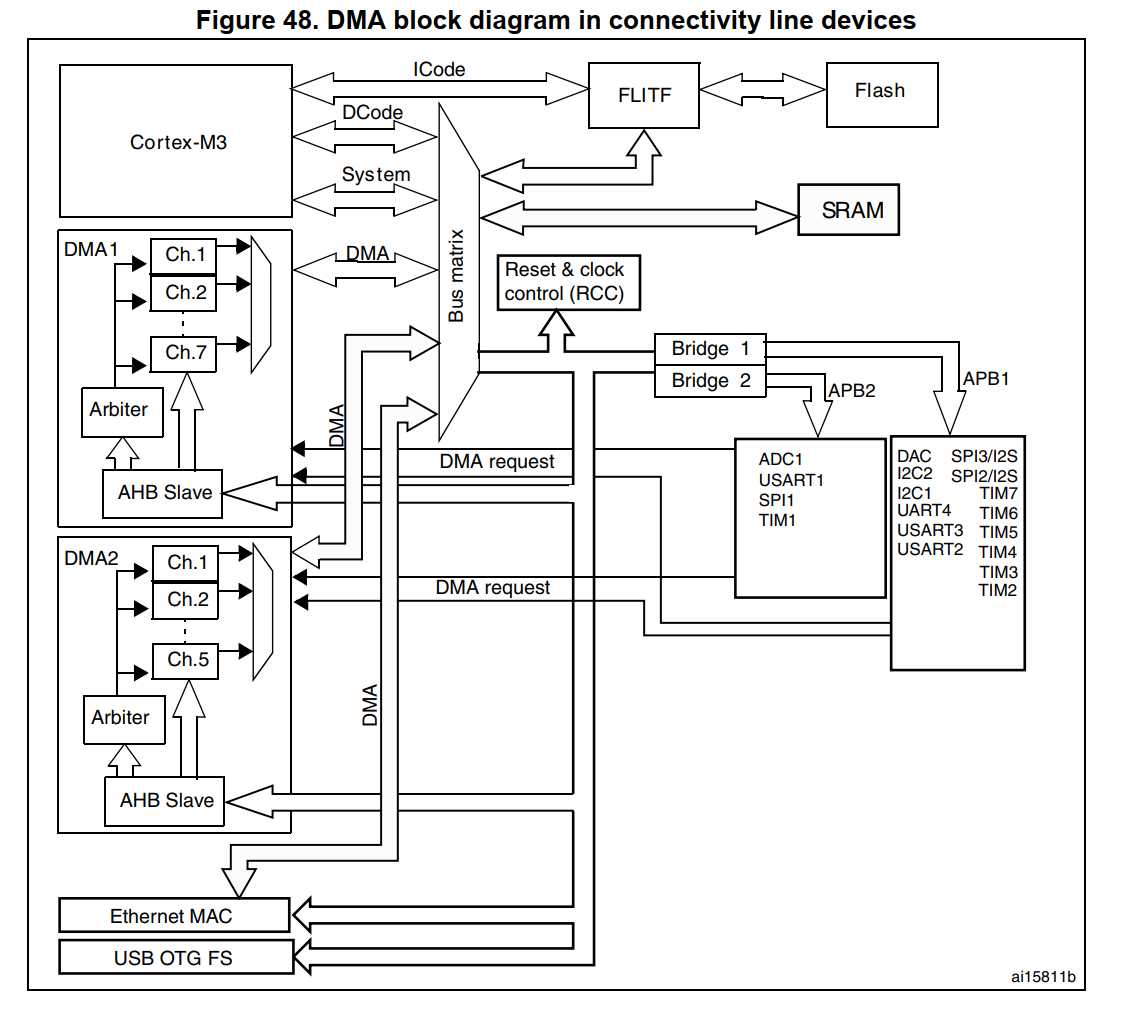

上图就是DMA的模块图,可以看出模块与存储器之间的数据传输可以不经过CPU。

13.3 DMA功能描述

DMA控制器通过与Cortex-M3内核共享系统总线执行存储器数据的直接传输。

当DMA请求与CPU针对相同的目标点(存储器或者外设)时,

DMA请求可能会使CPU访问系统总线停止几个周期。

总线矩阵实现循环调度,从而保证CPU能占用至少一半的系统总线带宽。

13.1 DMA事务

时间发生后,外设向DMA控制器发送一个控制信号。

DMA控制器根据通道的优先级处理请求。

只要DMA控制器访问外围设备,DMA控制器就会给外设发送一个响应。

当外设接收到DMA控制器的响应,外设会释放它的请求。

一旦请求被外围设备拒绝,DMA控制器会停止响应。

如果有更多的请求,外设会开始下一个事务。

综上所述,每个DMA包含包含3个操作:

从外围数据寄存器或内存地址加载数据,

通过一个内部的当前外设或存储器地址寄存器。

13.2 仲裁者

13.3 DMA通道

13.4 数据宽度、数据对齐方式以及大小端模式都是可编程的

13.5 错误管理

13.6 中断

13.7 DMA请求映射

13.4 DMA寄存器

原文:https://www.cnblogs.com/QQ2962269558/p/12342330.html