在编写代码时候经常会使用到上升沿检测或则下降沿检测,这个时候使用寄存器的方式来进行检测:通过检测当前信号与上一个时刻的信号对比便可以知道是上升沿还是下降沿。

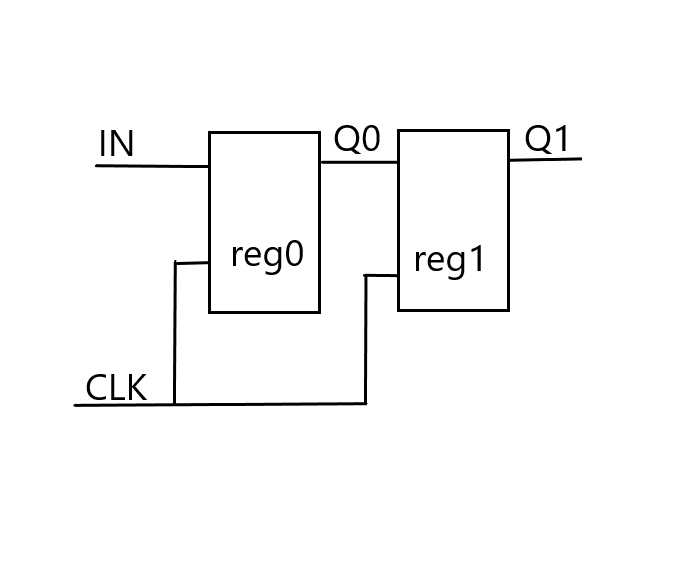

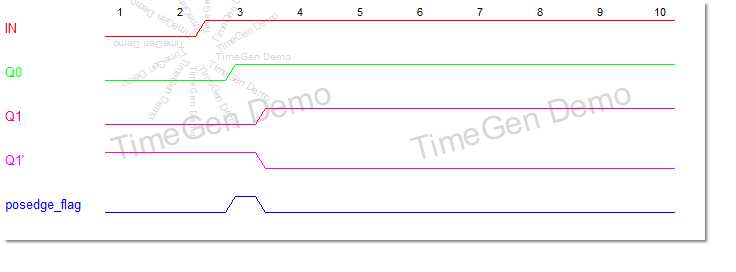

上升沿检测的寄存器输出波形:

下降沿检测的寄存器输出波形:

代码实现:

module top ( input clk_50MHZ ,//系统时钟50M input rst_n ,//系统复位 input key_in ,//按键 output key_posedge,

output key_negedge

); reg key_temp0 ;//用于按键上一次状态存储 reg key_temp1 ;//用于按键当前状态存储 //=============================================================================== // //边沿检测,采用寄存器方式。 // //=============================================================================== always@(posedge clk_50MHZ or negedge rst_n) begin if(!rst_n) begin key_temp0<=1‘b0; key_temp1<=1‘b0; end else begin key_temp1<=key_in; key_temp0<=key_temp1; end end assign key_posedge=(!key_temp0)&key_temp1; assign key_negedge=(!key_temp1)&key_temp0; endmodule

原文:https://www.cnblogs.com/xiaozhu5208/p/12361978.html