makefile命名: makefile 或者 Makefile

1个规则

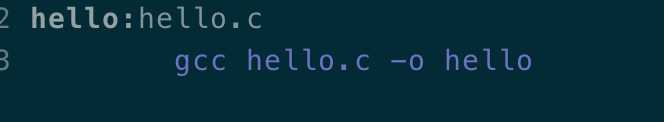

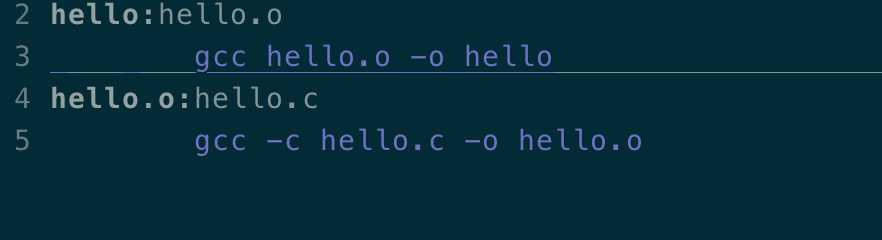

目标:依赖条件

目标的时间必须晚于依赖条件的时间,否则就会更新目标

依赖条件如果不存在,找寻新的规则去产生依赖

makefile会默认把第一条指令当做最终目标

可以使用ALL:a.out,来指定最终的生成目标

2个函数

3个自动变量

$@: 在规则命令中表示规则中的目标

$^: 在规则的命令中,表示所有的依赖条件

$<:在规则的命令中,表示第一个依赖条件,如果该变量应用在模式规则中,它可以依赖条件列表中依赖依次去除,套用模式规则。

src = $(wildcard *.c) #add.c sub.c div1.c hello.c

obj = $(patsubst %.c, %.o, $(src)) # add.o sub.o div1.o hello.o

ALL:a.out

a.out:$(obj)

gcc $^ -o $@

hello.o:hello.c

gcc -c $< -o $@

add.o:add.c

gcc -c $< -o $@

sub.o:sub.c

gcc -c $< -o $@

div1.o:div1.c

gcc -c $< -o $@

clean:

-rm -rf $(obj) a.out模式规则:

%.o:%c可以替换下面所有

%.o:%.c

gcc -c $< -o %@

hello.o:hello.c

gcc -c $< -o $@

add.o:add.c

gcc -c $< -o $@

sub.o:sub.c

gcc -c $< -o $@

div1.o:div1.c

gcc -c $< -o $@静态模式规则:

伪目标

可以加警告和调试

myargs = -Wall -g

gcc -c $< -o $@ $(myargs)

使用makefile入门使用方法,一个规则,两个函数,三个自动变量

原文:https://www.cnblogs.com/fandx/p/12518191.html