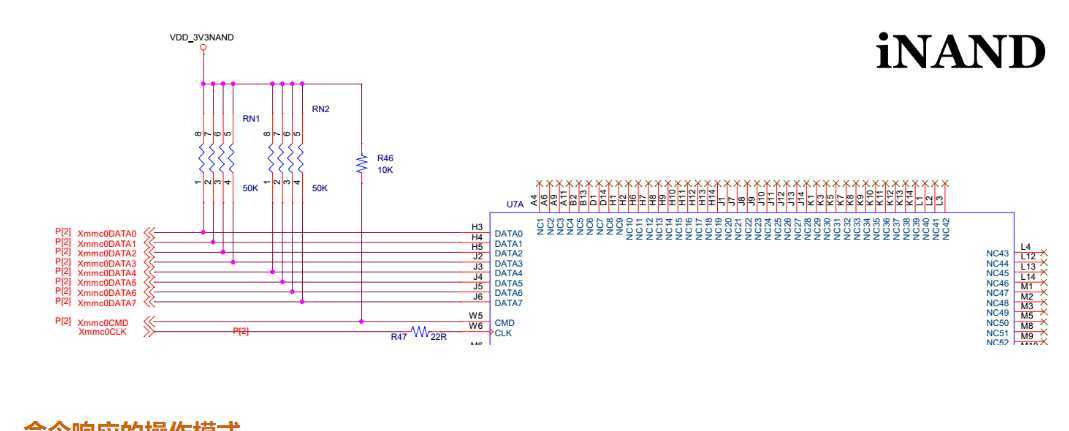

INAND MMC时钟控制

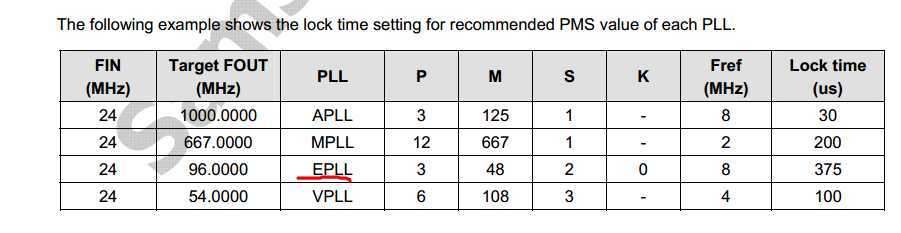

EPLL 外设倍频器

ldr r0, =0xE0100000 ldr v1, =0x2D0 ldr v2, =0x12C0 ldr v3, =0x2328 ldr v4, =0x960 str v1, [r0, #0x00] str v2, [r0, #0x04] str v3, [r0, #0x08] str v4, [r0, #0x0c]

代入可算出SCLKEPLL 96MHZ

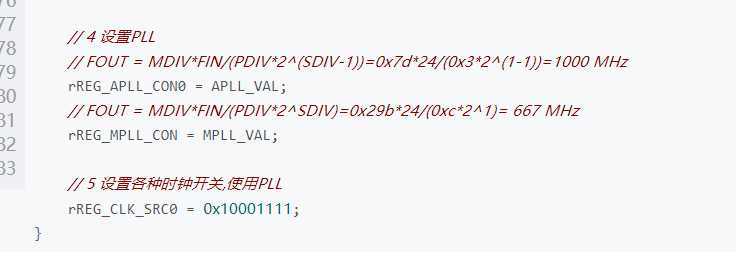

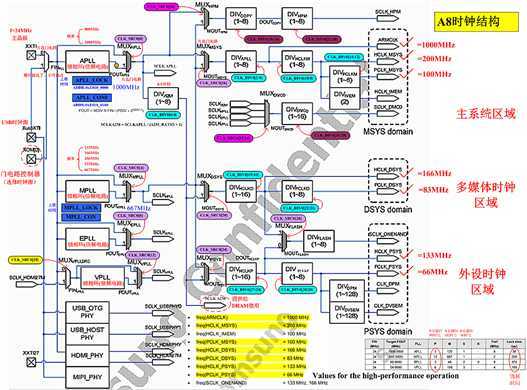

在寄存器中,clock source x - 设置MUX开关,clock divider control - 设置分频系数

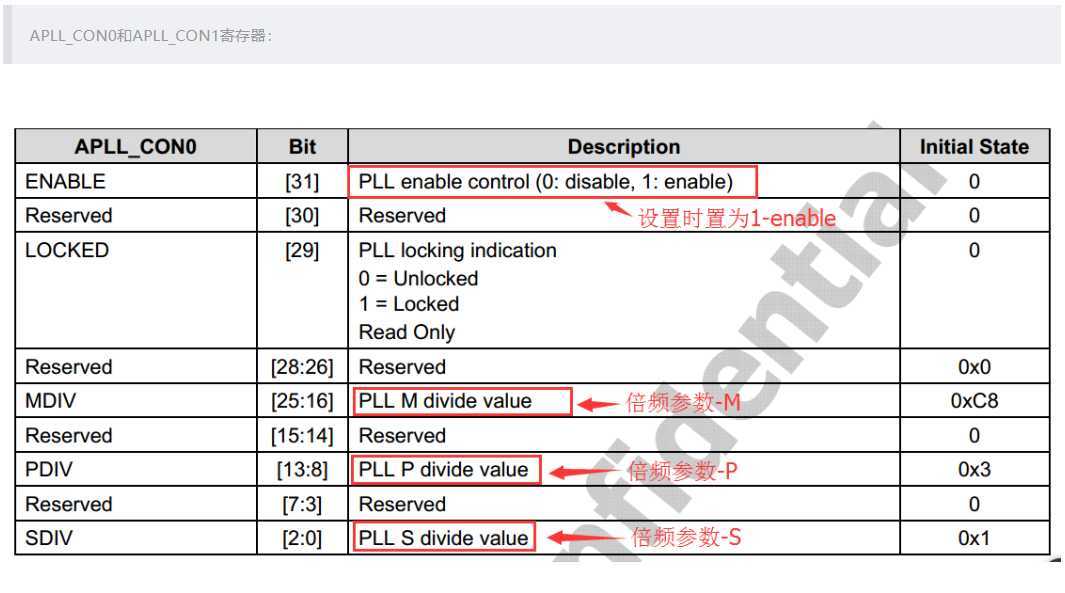

xPLL_CON/xPLL_CON0/xPLL_CON1 寄存器:主要是用来打开/关闭PLL电路,设置PLL的倍频产生,查看PLL锁定状态等

CLK_SRC4 MMC MUX时钟配置 CLK_DIV4 分频配置

CLK_MUX_STATn(n:0~1)寄存器:查看MUX的状态是否已经完成还是在进行中

总结:最重要的有三类寄存器,分别是CON、SRC、DIV。其中CON决定PLL倍频多少,SRC决定走哪一条路,DIV决定分频多少。

原文:https://www.cnblogs.com/ben-sen/p/12608968.html