,

(1)什么叫推挽输出

(2)原理

如上图所示,INT为输出数据寄存器(ODR),当INT为高电平时,经过反向器,2处为低电平,则G处为低电平,Us为VDD输入3.3V,此时Ug <Us,PMOS管导通,out输出引脚被拉高,为高电平,输出3.3V;

若INT为低电平时,经过反向器,2处为高电平,此时G点位高电平,Ug>Us,NMOS管导通,out引脚被拉低为低电平。

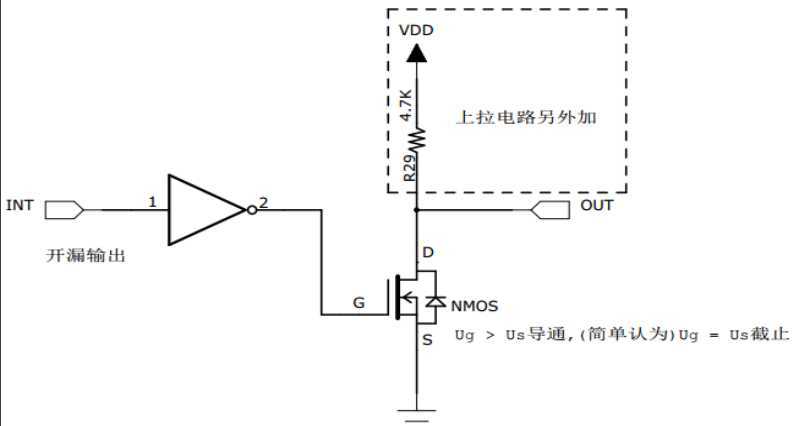

(1)什么是开漏输出?

(2)原理

如上图所示,输出数据寄存器(ODR)为高电平时,经过反向器,2处为低电平,此时Ug=Us截止,NMOS没有导通,上拉电路中的VDD让out输出为高电平;

当输出寄存器(ODR)为低电平时,经过反向器,2处为高电平,此时Ug>Us,NMOS导通,out被拉低为低电平。

原文:https://www.cnblogs.com/yuanqiangfei/p/12748046.html