欢迎大家关注我的微信公众账号,支持程序媛写出更多优秀的文章

串并转换是高速流水处理重要的设计技巧之一,串并转换的方法也多种多样,根据数据的顺序和数量要求,可以选择寄存器、双口RAM、SRAM 、SDRAM、FIFO等实现,对于数量比较少的设计,可以采用移位寄存器设计。

在工程应用中,如何体现串并转换设计思想呢?

怎样才能提高系统的设计速度呢?

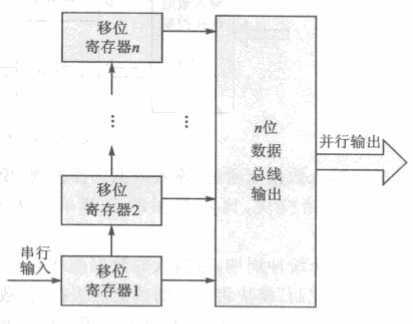

我们可以先来做一个串并转换的设计框图, 如图所示,串行输入的数据通过FPGA内部的n个寄存器后,最后并行输出的是一个n位宽的并行总线数据。

注意:(当然,串行输入的数据位宽不局限于1位的数据,也可以是m位的,得到的数据位宽即为n*m)

移位一般是要有时钟做同步的,也就是说,n个时钟采样到的串行数据需要在n个时钟周期后以并行方式输出,这是最基本的传入并出设计思想,对于串行接口大行其道的高速传输领域,这种简单的转换也是接口芯片的重要任务之一,但从FPGA的角度来看,串并转换又有着更深的意义,串并转换正是面积换速度思想的体现。

【FPGA技巧篇二】FPGA设计的四种常用思想与技巧之二 :并串转化

原文:https://www.cnblogs.com/streetlive/p/12862538.html