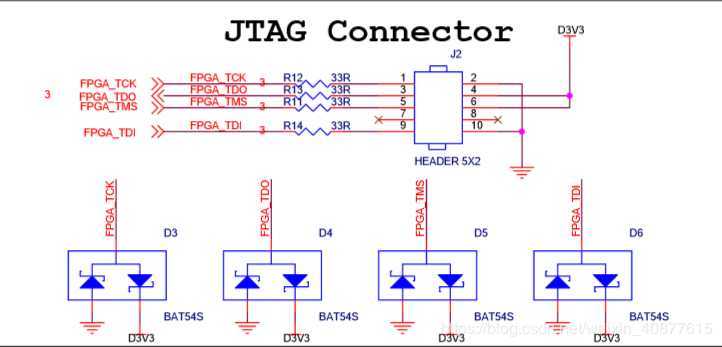

手头上两块FPGA开发板(黑金和正点原子)的FPGA接口部分设计略有不同,黑金的开发板特别在接口上加了保护电路。如图:

使用BAT54钳位。

查了下网上确实有人反映ALTERA的FPGA的JTAG接口IO容易损坏,有人怀疑了ALTERA为了省成本将内部钳位电路优化掉了,导致这一原因,所以外部加上这部分钳位电路。

1.这里就有一个疑问,一般的接口保护电路多采用TVS管来做。那这里是否可以用TVS来保护?

原理上,我想是可以的。但在TVS管的元器件选型上,竟然很难找到5V以下的TVS管。

2.为什么没有5V以下的TVS管?

这是网上答案------10V是最大脉冲峰值电流情况下的最大箝位电压,一般情况下会低于这个值。

国标规定的冲击波形持续时间都是μs级的,也就是说后端电路承受的10V左右的电压只有几十个μs左右,一般情况下是可以承受的,不然3.3V的TVS管肯定卖不出去了

TVS的箝位电压不可能像稳压管那么精确

所以关于保护电路就可以这样分析,芯片一般内部自带了钳位保护电路,而接口部分使用TVS管。当外部静电放射ESD,由TVS管进行初级吸收,钳位电路次级保护。

原文:https://www.cnblogs.com/xuzhongjie/p/12883351.html