我们知道nand没有独立地址线,cpu无法直接访问nand上的指令,所以nand不能片上执行。那么为何程序还能支持nand启动的呢?

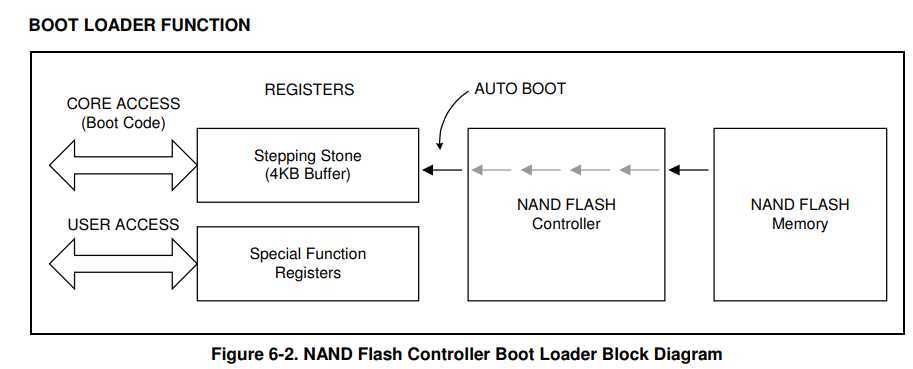

为了支持NAND启动,S3C2440A配备了一个称为“ Steppingstone”的内部SRAM缓冲区,容量为4K。 开机时,Nandflash中的前4K数据将被加载到Steppingstone中,而引导代码将被加载到SRAM中将被执行,如下图所示:

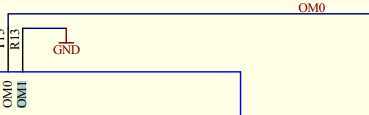

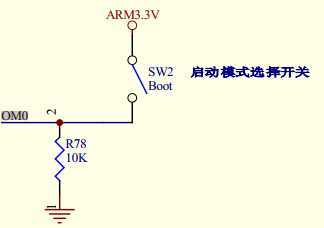

我们知道s3c2440支持2种boot方式,nand或者nor,那么需要配置OM引脚来设置引导方式,如下图:

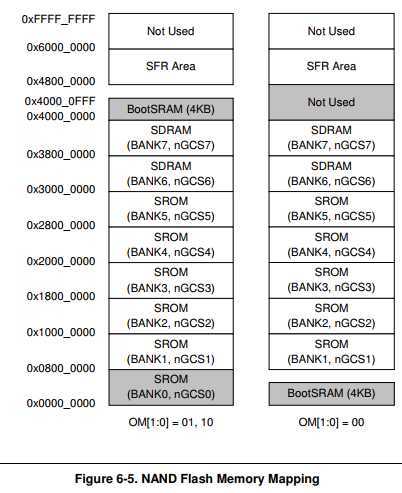

内存控制器的地址映射表如下:

我们得知OE1接地,OM0接了一个开关SW2,那么我们的OE0的电平状态由SW2开关决定:

当SW2闭合,OM0=1, OM[1:0]=10, 0地址对应nor,那么从nor启动。

当SW2断开,OM0=0, OM[1:0]=00, 0地址对应bootSRAM(4K),那么0地址对应该SRAM, 那么从nand启动。

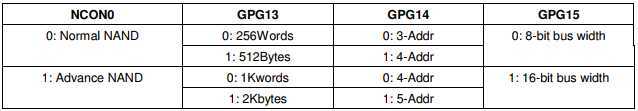

当上电启动时,NAND Flash 控制器将通过下面的引脚配置来获取连接的 NAND Flash 的信息。

NCON:NAND Flash 存储器选择(普通/先进)

0:普通 NAND Flash(256 字或 512 字节页大小,3 或 4 个地址周期)

1:先进 NAND Flash(1K 字或 2K 字节页大小,4 或 5 个地址周期)

GPG13:NAND Flash 存储器page size选择

0:页=256 字(NCON=0)或页=1K 字(NCON=1)

1:页=512 字节(NCON=0)或页=2K 字节(NCON=1)

GPG14:NAND Flash 存储器地址周期选择

0:3 个地址周期(NCON=0)或 4 个地址周期(NCON=1)

1:4 个地址周期(NCON=0)或 5 个地址周期(NCON=1)

GPG15:NAND Flash 存储器总线宽度选择

0:8 位宽度

1:16 位宽度

如下表所示更直观:

s3c2440裸机-nandflash编程(二. nand控制器)

原文:https://www.cnblogs.com/fuzidage/p/13020052.html