一、实验硬软件环境:

二、实验内容:

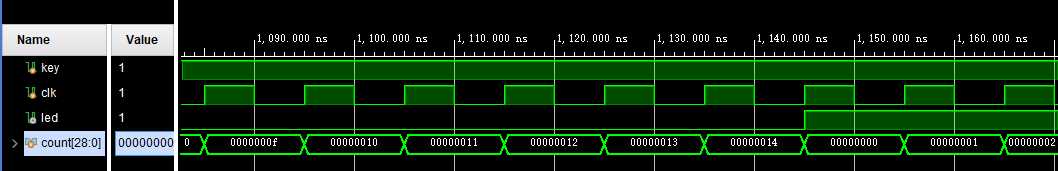

实现的电路功能为:当开关开启,led点亮;开关关闭,则led灯关闭,在设计文件和测试文件中,在合适的位置,分别插入$monitor、$display、$stop以及$finish语句,观察simulation的结果。

三、 具体实现

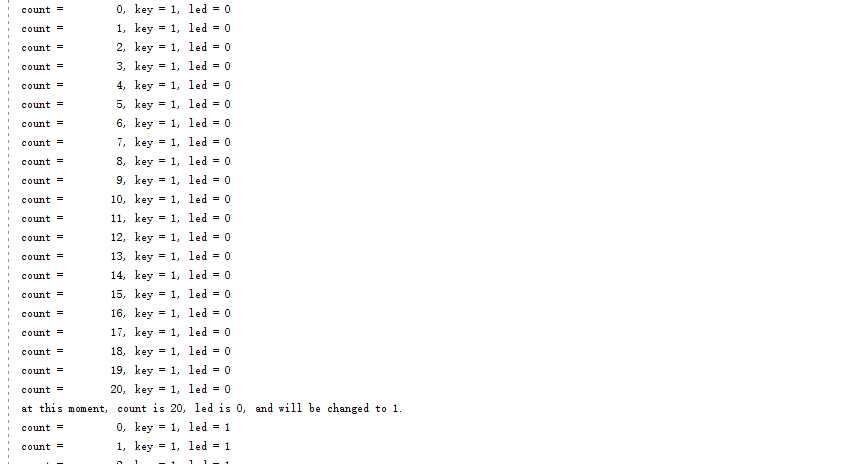

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2020/08/17 18:02:59 7 // Design Name: 8 // Module Name: led 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module led( 24 input key, 25 input clk, 26 output reg led 27 ); 28 29 reg [28:0] count; 30 31 always @(posedge clk) 32 begin 33 if(key == 0) 34 count <= 29‘b0; 35 else 36 if(count == 20) 37 count <= 29‘b0; 38 else 39 count <= count + 1; 40 end 41 42 always@(posedge clk) 43 begin 44 if(key == 0) 45 led <= 0; 46 else 47 if(count == 20) 48 begin 49 led <= ~led; 50 $display("at this moment, count is 20, led is %b, and will be changed to %b.", led, ~led); 51 end 52 else 53 led <= led; 54 end 55 endmodule

1 `timescale 1ns / 1ps 2 ////////////////////////////////////////////////////////////////////////////////// 3 // Company: 4 // Engineer: 5 // 6 // Create Date: 2020/08/17 18:19:52 7 // Design Name: 8 // Module Name: led_tb 9 // Project Name: 10 // Target Devices: 11 // Tool Versions: 12 // Description: 13 // 14 // Dependencies: 15 // 16 // Revision: 17 // Revision 0.01 - File Created 18 // Additional Comments: 19 // 20 ////////////////////////////////////////////////////////////////////////////////// 21 22 23 module led_tb; 24 reg key; 25 reg clk; 26 wire led; 27 28 led uut(.key(key), .clk(clk), .led(led)); 29 30 initial 31 begin 32 $monitor("count = %d, key = %d, led = %d", uut.count, uut.key, uut.led); 33 34 key = 0; 35 clk = 0; 36 37 #100 key = 1; 38 39 end 40 41 always #5 clk = ~clk; 42 endmodule

1 set_property PACKAGE_PIN V17 [get_ports key] 2 set_property IOSTANDARD LVCMOS33 [get_ports key] 3 set_property PACKAGE_PIN U17 [get_ports led] 4 set_property IOSTANDARD LVCMOS33 [get_ports led]

原文:https://www.cnblogs.com/mantha/p/13521080.html