//单端口RAM--读写总线,读写数据总线,8bit*16

//通过进行地址编码表示RAM深度。可修改其地址位宽改变其深度。 module test ( input clk, input rst, input wr_en,//wr_en=1时,为写操作。wr_en=0时,为读操作。 input [3:0]w_addr, input [3:0]r_addr, input [7:0]w_data, output reg [7:0]r_data ); reg [7:0]mem[15:0]; always @(posedge clk or negedge rst) begin if(!rst) begin r_data <= ‘b0; end else if (wr_en) begin mem[w_addr] <= w_data; end else if (~wr_en) begin r_data <= mem[r_addr]; end else begin r_data <= r_data; end end endmodule

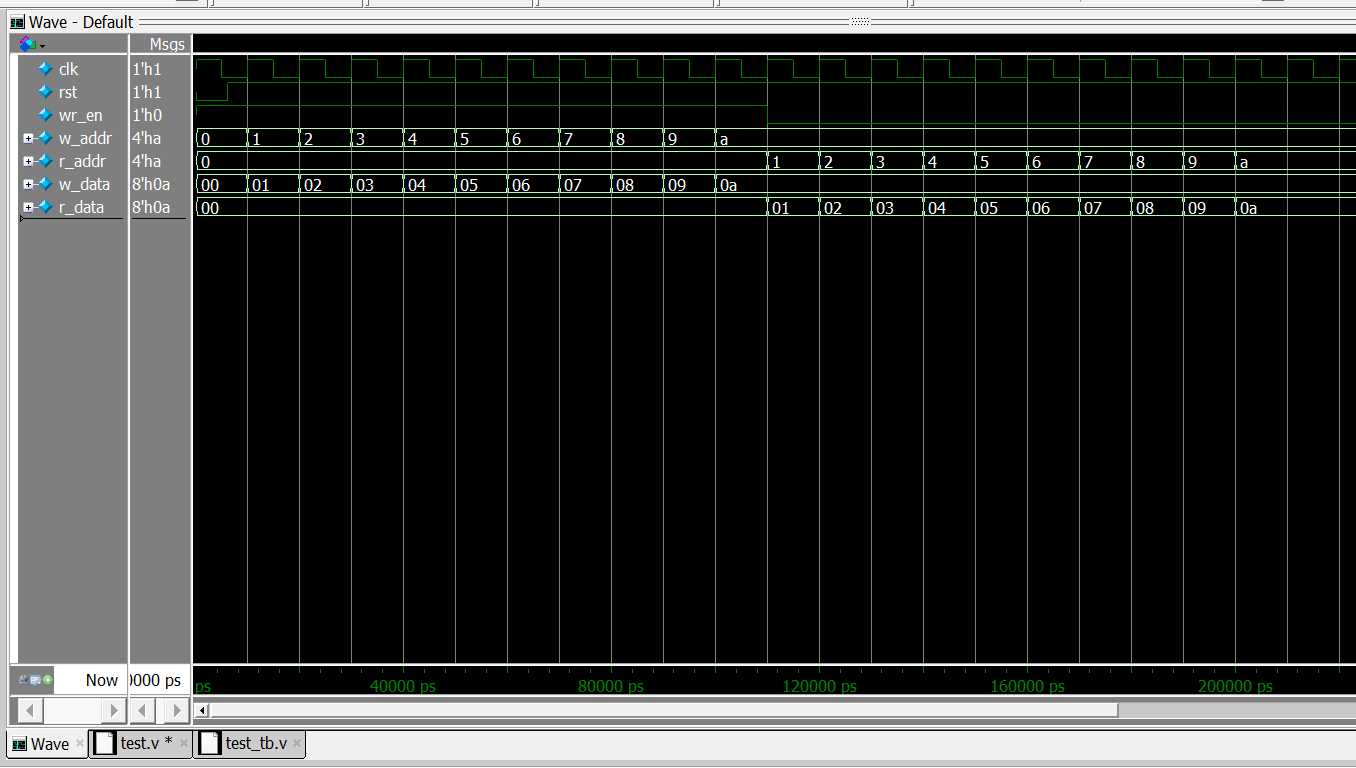

测试用例:

`timescale 1ns/10ps module test_tb; reg clk; reg rst; reg wr_en; reg [3:0]w_addr; reg [3:0]r_addr; reg [7:0]w_data; wire [7:0]r_data; test u1( .clk(clk), .rst(rst), .wr_en(wr_en), .w_addr(w_addr), .r_addr(r_addr), .w_data(w_data), .r_data(r_data) ); initial begin w_addr = ‘b0; r_addr = ‘b0; w_data = ‘b0; clk = 1‘b1; rst = 1‘b0; wr_en = 1‘b1; #6; rst = 1‘b1; end always #5 clk = ~clk; initial begin wr_en = 1‘b1; #110; wr_en = 1‘b0; #110; end initial begin #10; repeat(10) begin w_addr = w_addr + 1‘b1; #10; end repeat(10) begin r_addr = r_addr + 1‘b1; #10; end end initial begin #10; repeat(10) begin w_data = w_data + 1‘b1; #10; end end endmodule

原文:https://www.cnblogs.com/shadow-fish/p/13556772.html