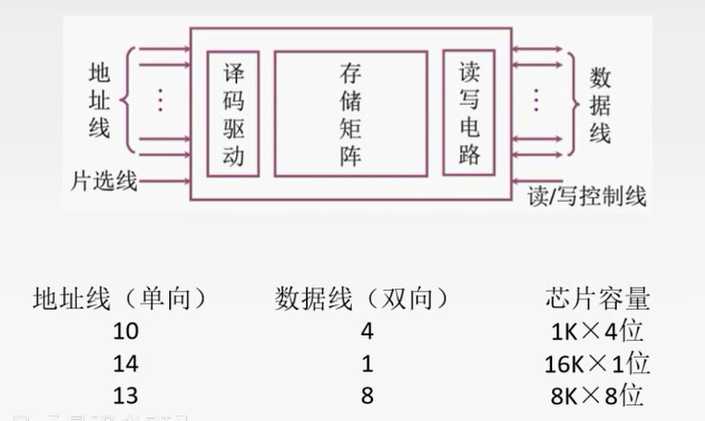

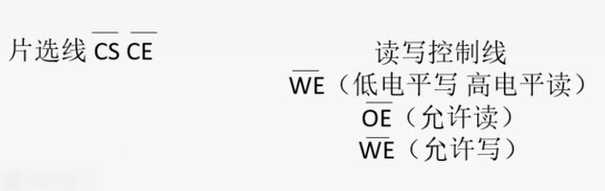

片选线:确定哪一个存储芯片被选中

上面有一杠:低电平有效

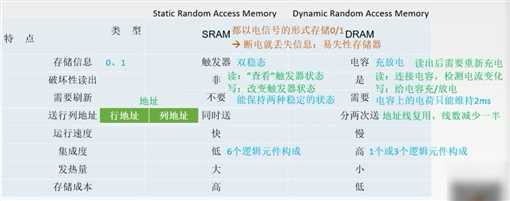

static random access memory

DRAM:dynamic random access memory

随机存储存储器

半导体材料,构成不同的电路

一旦断电立马丢失信息。

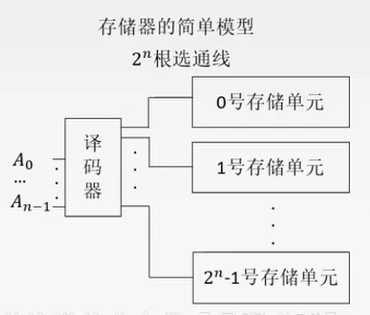

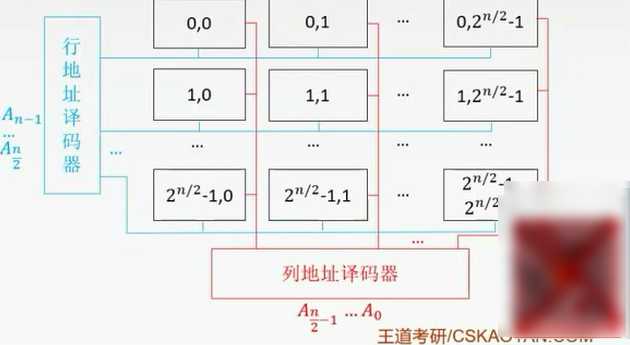

以前的那个太多条线了

拆分为行列地址(DRAM行、列地址等长)

存储单元排列成2^{n/2} * 2^{n/2} 的矩阵

减少了选通线的数量。

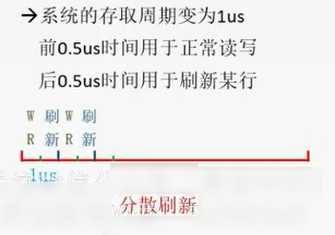

思路一:每次读完都刷新一行(分散刷新)

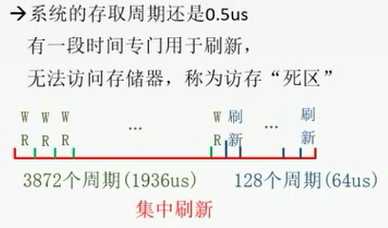

思路二:2ms内集中安排时间全部刷新(集中刷新)

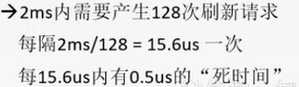

思路三:2ms内每行刷新1次即可(异步刷新)

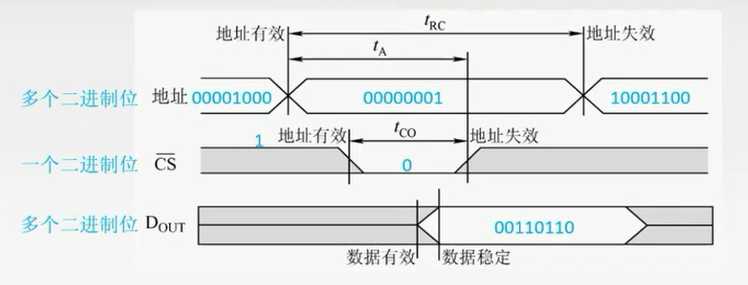

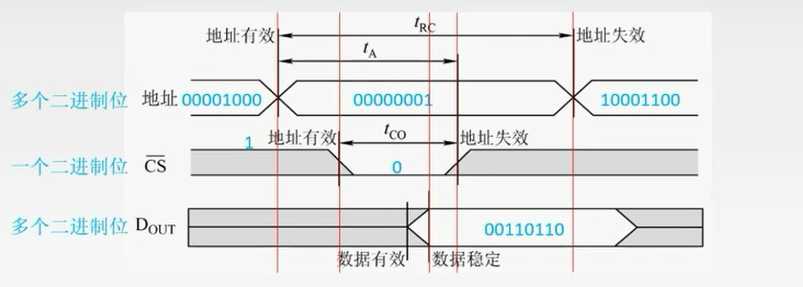

首先给一个地址信号,地址产生效果,地址线有快有慢,需要等待稳定。

经过一段时间后片选线才能有效。找到读的是哪一个存储元的信息。

等多一段时间,进行数据的读操作,

数据线上稳定了有信号,开始读。数据线稳定输出,

完全读出,片选线才失效(保持到数据稳定输出)。

等多一段时间,地址信号才撤回,下一个地址。

如果读写控制线为1根,则整个读过程中WE(一杠)为高电平

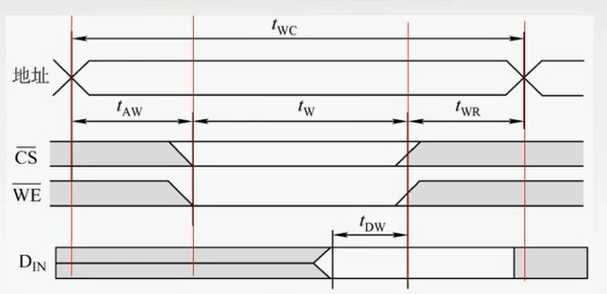

首先给一个地址,等待地址稳定后

随机存取

易失性,一断电丢失

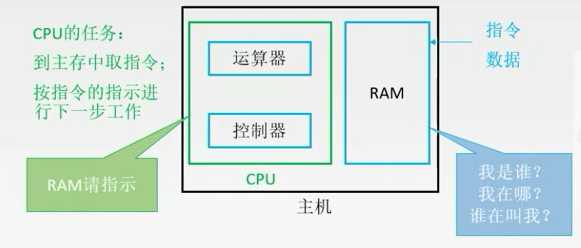

CPU任务:到主存中取指令;按指令的指示进行下一步工作

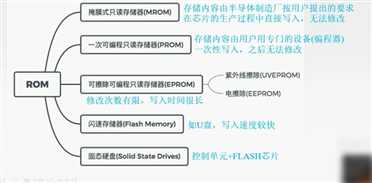

ROM断电之后也不会丢失。

先把辅存里的OS调到ROM

为什么不全用ROM?因为有时候还是要写的

非易失性:ROM

原文:https://www.cnblogs.com/jev-0987/p/13561065.html