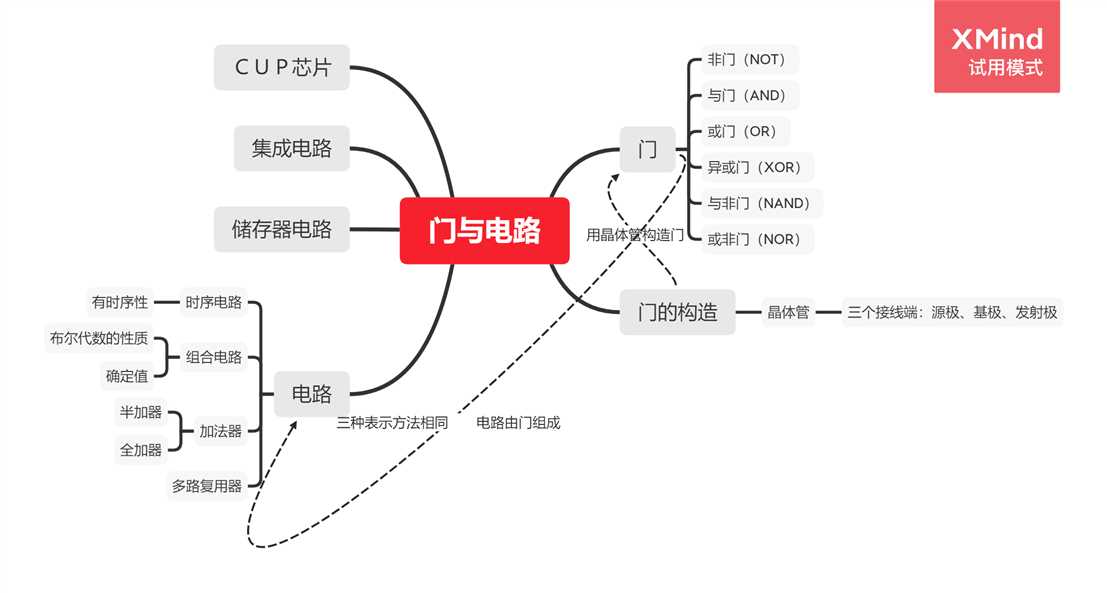

门可以构成电路,而电路是计算机的基础部分。门是可以对电信号执行基础运算的设备,门有很多类型,这一张我们学习了六种最简单的类型。每种类型都执行一个特定的逻辑函数。

电路是由们组合而成的,在不同门的组合下,电路可以执行更为复杂的任务,进而使计算机能处理跟复杂的问题。电路可以执行运算、存储可以和其他电路再组成成新的电路,电路中的门所输出的值通常是作为一个或者多个门的输入值,门与门间传递的是电流,而传递在电路中的电流是经过许多门精心设计和关联后所控制的。

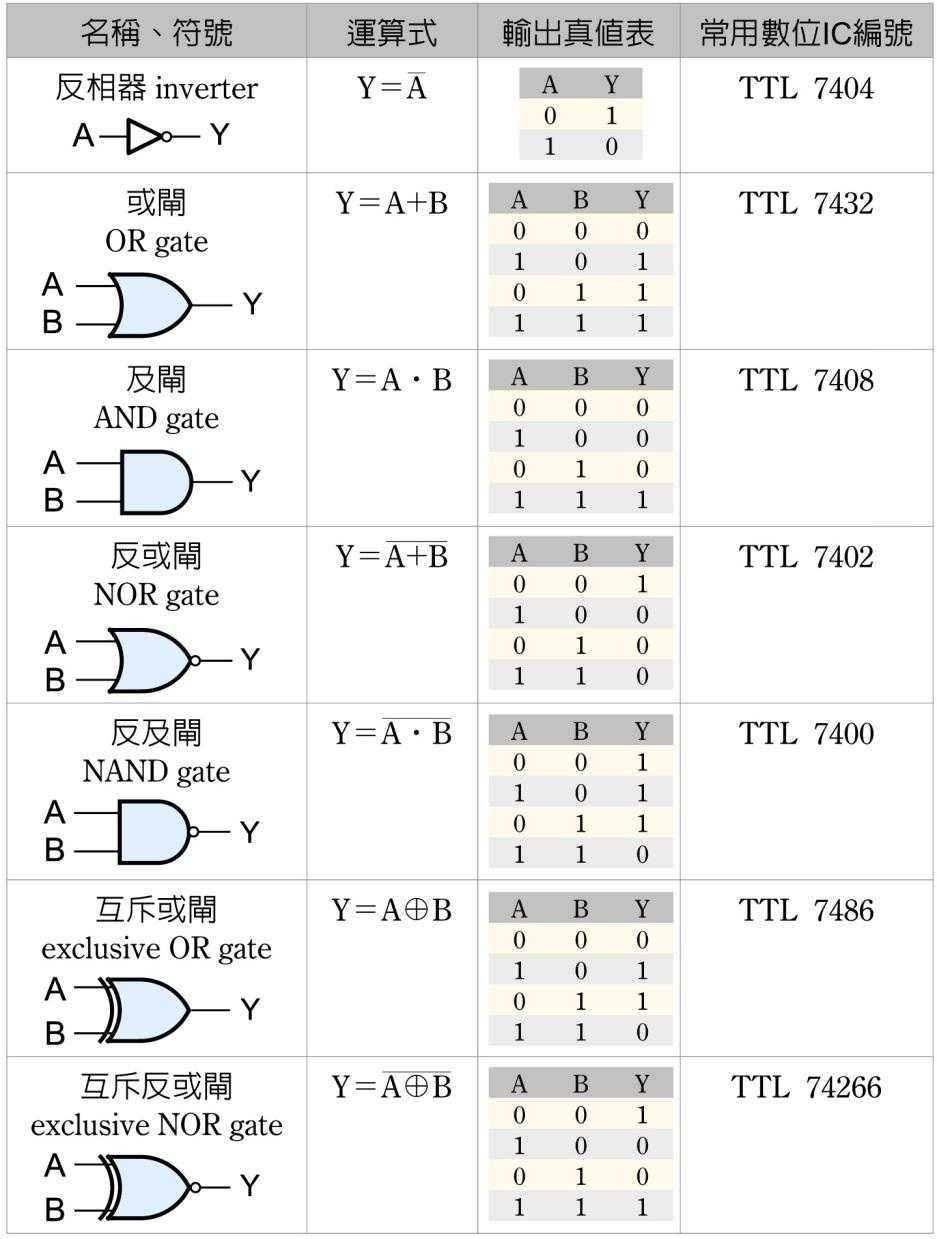

门和电路通常有三种表示方法,分别是布尔代数、逻辑框图和真值表。①布尔代数是一种表示二值函数的数学方法,②逻辑框图则是将电路图形化更直观的表现门的结构,每种门都有他自己专用的符号,③真值表是通过表格一一列举出所有可能的输入值和对应的输出值的一种图表表示方法(唯一能表示所有情况的方法)。

计算机中的门有时又叫作逻辑门(logic gate),为每个门都执行一种逻辑函数。每个门接收一个或多个输入值,生成一个输出值,由于我们处理的是二进制信息,所以每个输入和输出值只能是0(对应低电平信号)或1(对应高电平信号)门的类型和输入值决定了输出值。

非门(NOT)所代表的是将输入的高电平转换成低电平的逻辑门,同理它也可以将低电平转换成高电平,总结起来就是输出反信号,所以它有时也被叫做逆变器,与其他五个门不同的是它只有一个输入值。

与门(AND)与门拥有两个输入信号,当两个输入信号都为高电平(1)输出的值才为高电平(1),其他情况输出的都为低电平(0)。

或门(OR)在输入都为0的时候输出是0;否则输出为1.

异或门(XOR)又叫做同或门,只有在两个输入信号相同时才会输出0;否则输出为1。

与非门(NAND)与非门可以看作是与运算求逆,与非门和与门输入值相同时,输出值相反。

或非门(NOR)同理或非门相当于是对或运算的求逆。

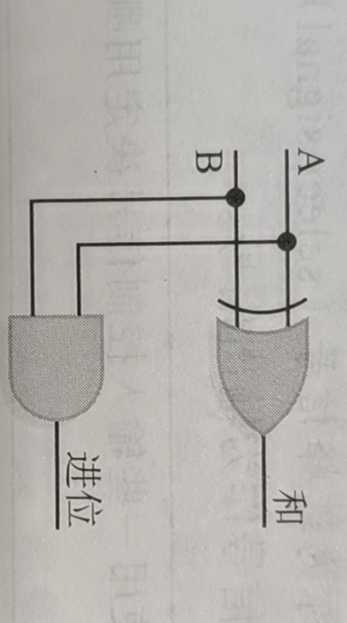

注意与门和或门逻辑框图符号的区别,以及各种布尔表达式的正确写法。

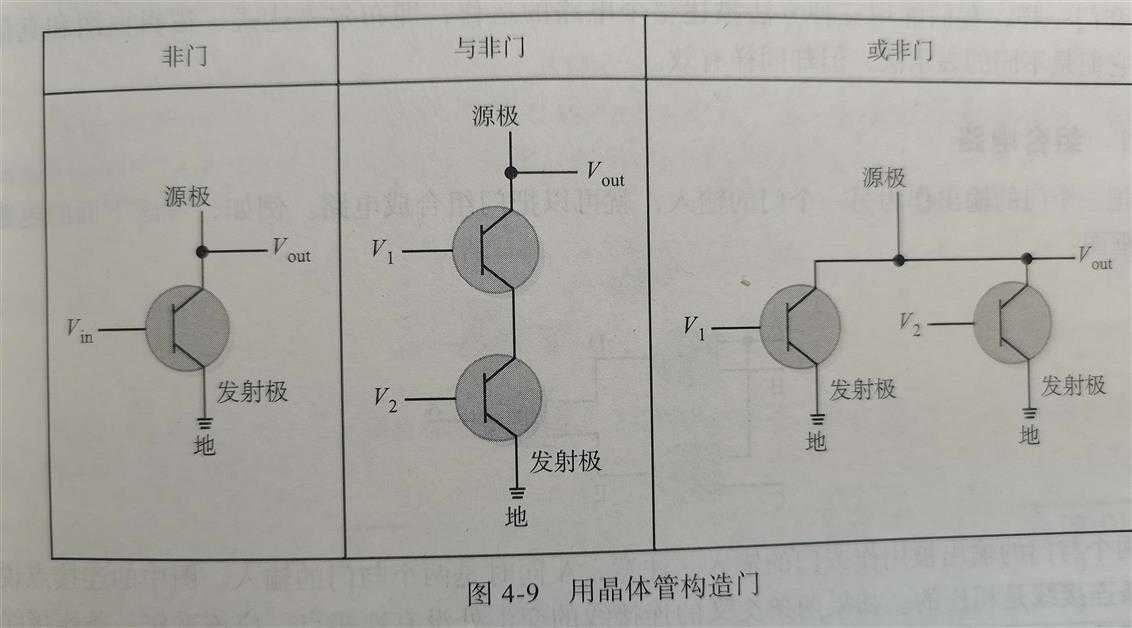

晶体管具有三个接线端,即源极、基极和发射极,发射极通常被连接到地线,。在计算机中源极制造的是高电平,约为5伏,基极值控制的门决定了是否把源极接地如果源极信号接地了,它将被降低到0伏。如果基极没有使源基极信号接地,源极信号仍然是高电平。

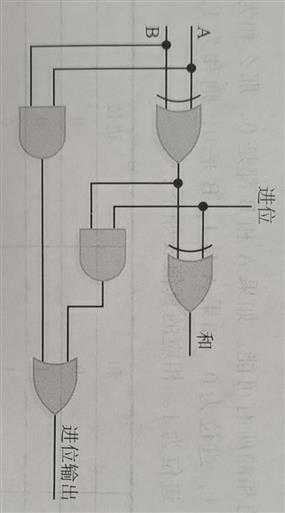

用晶体管构造门如图:

如我们在这一章的前面所述,与门生成的结果和与非门的完全相对。因此,要构造与门,只需要把与非门的结传递给一个变器(非门1)即可。这就是为什么与门比与非门的构造复杂:与门需要三个晶体管,其中两个用于构造与非门,一个用于构造非门。或非门或门之间存在同样的关系。

电路可以分为两大类,一种是组合电路,一种是时序电路,组合电路输入值对应了特定的输出值,而时序电路是输出是输入值和电路当前状态的函数的电路。

和门一样,我们能用三种方法描述整个电路的运作,即布尔表达式、逻辑框图和真值表。

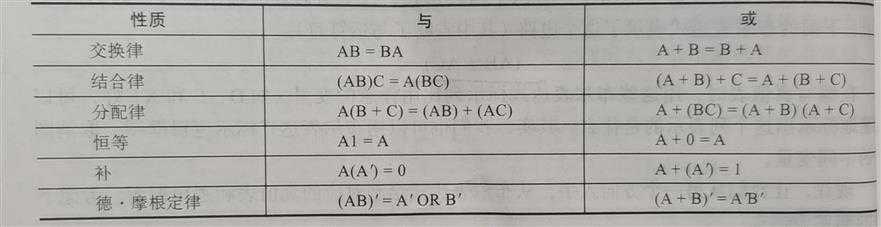

电路间输入输出的线路的连接使得门与门之间“共同协作”完成许多多样的功能,并且输入值不仅限于一个或者两个,多个输入值组成的门将处理更为复杂的逻辑。其中布尔代数有许多重要性质:

德·摩根定律需重点学习

加法器是指专门执行对二进制加法运算的专用电路。

半加器是由异或门和与门组成,可以计算两个数位的和并生成正确进位的电路。由于半加器不会讲进位输入的数值考虑在内,所以只能计算两个数位的和,

而考虑进位输入的电路叫做全加器(可以由两个半加器构成)

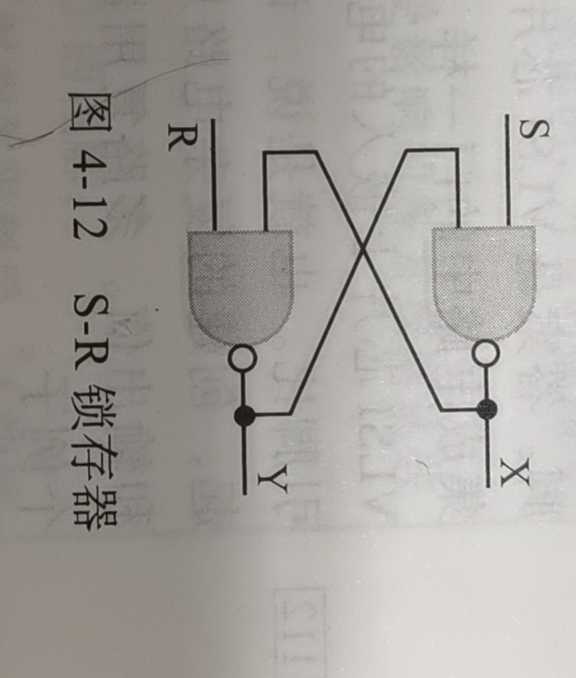

存储器电路有很多种,书上所了解到的S-R锁存器是使用两个与非门(S与R)互相交错输入、输出的电路,并有两个最终输出端(X和Y)。通过对两个与门的控制,S-R锁存器可以保留其本身的数值。例如S暂时设置为0,保持R为1,就可以把锁存器设置为1,如果S为0,则X变为1。此时只要将S恢复为1,S-R锁将保持锁定状态。

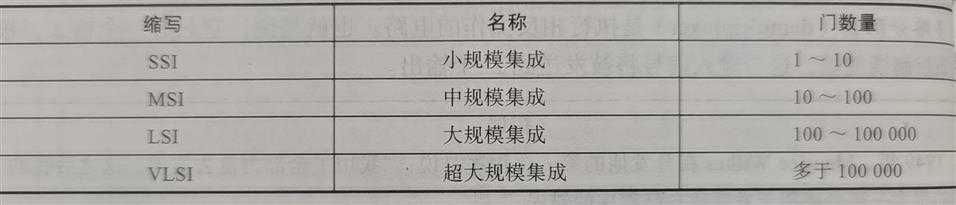

集成电路是嵌入了多个门的硅片,根据门的数量,从小规模集成到超大规模集成。

CPU芯片是具有大量引脚的高级电路,也被叫做中央处理器。

关键术语加法器(adder) 集成电路(integrated circuit)(也叫作芯片(chip))布尔代数(boolean algebra) 逻辑框图(logic diagram) 成只电路(circuit) 多路复用器(multiplexer) 电路等价(circuit equivalence)半导体(semiconductor) 组合电路(combinational circuit) 时序电路(sequential circuit) 全加器(full adder) 晶体管(transistor) 门(gate) 真值表(truth table) 半加器(half adder)

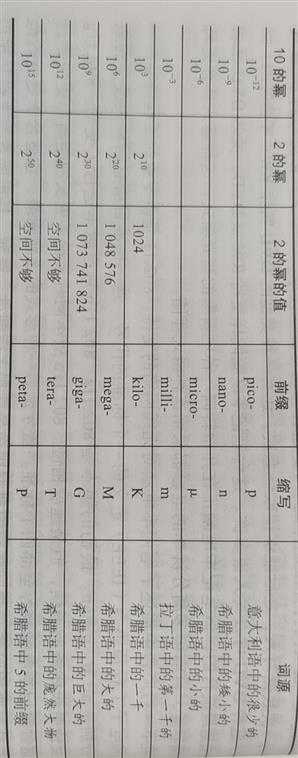

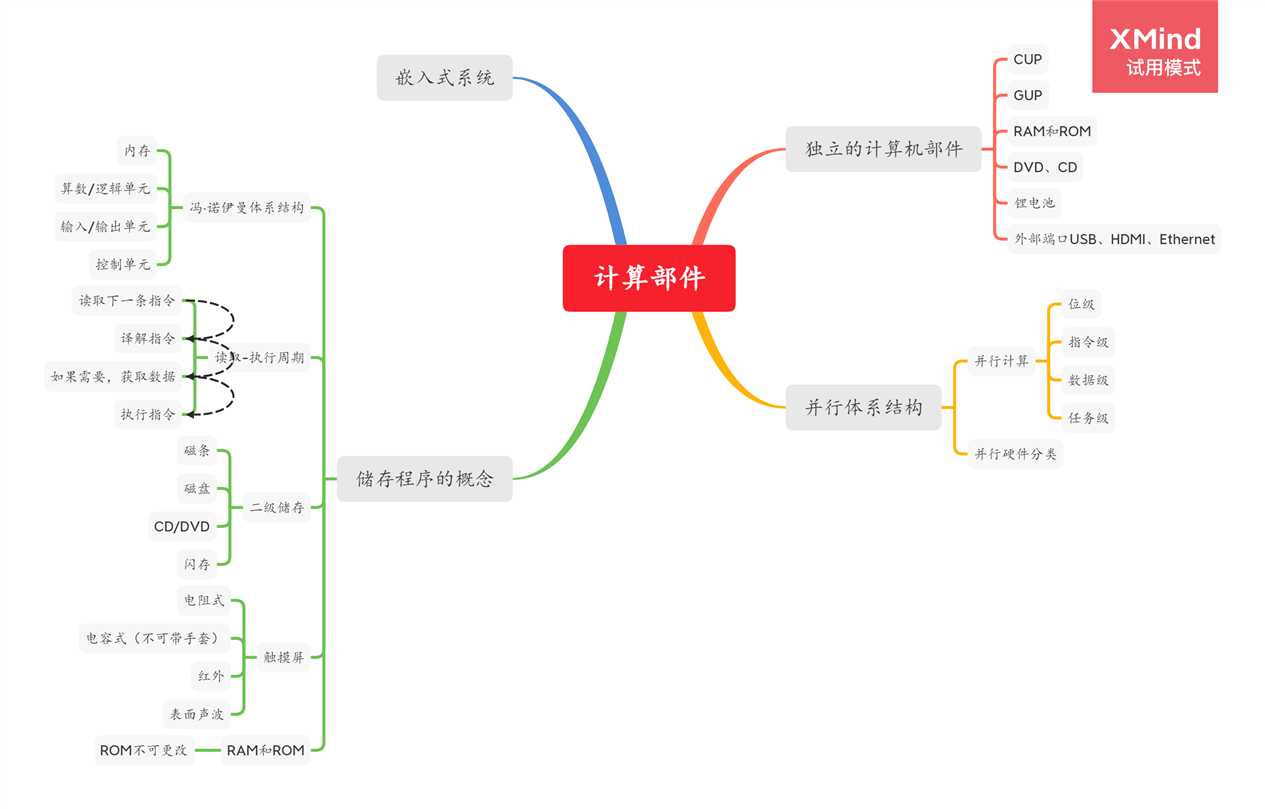

计算机中有很多部件,其中就包括:中央处理器(CPU)、显示器、随机访问存储器(RAM)、DVD等,这些部件共同辅助着电脑满足人们的办公生活娱乐需求。计算机中常用的前缀:

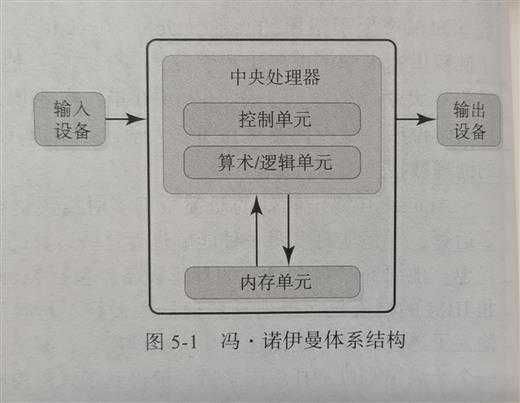

冯诺依曼结构是当今大多数计算机的底层体系结构,由5个主要部分组成:内存、算术/逻辑单元、输入设备、输出设备,内存负责存放数据和指令,算数/逻辑单元负责对数据执行算数和逻辑运算,输出单元将数据从计算机内部输出至外部世界,输入则是将外部信息输入计算机,控制单元负责监督其他部件的运行

。

在计算机中存在着数据处理周期,通过进行重复周期中的四个指令来进行正常的数据处理,四个步骤:读取下一条指令—译解指令—如果需要,获取数据—执行指令。

RAM和ROM,前者可以读写,而后者只能读取,不能更改,用于储存计算机启动自身需要的指令。

二级储存也是一种输入输出设备,主要包括磁带和磁盘。

闪存是一种可写入可擦除的非易失性计算机储存器

触摸屏包括:电阻式、电容式(不能用戴手套的手指触摸)、红外、表面声波

嵌入式系统作为大型系统的一部分,是为了完成小范围功能而专门设计的计算机。通常,一个嵌入式系统集成在单个微型处理器芯片上,程序被储存在ROM中,嵌入式操作系统无处不在,嵌入式系统通常包含操作系统,但更多的是用来完成专门的用途而将整个电路当作一个单独的程序实施。

并行体系联系到并行计算的四种一般的形式:位级、指令级、数据级和任务级。

位级是基于增加计算机的字长,使得能减少处理比字长更长的数值所需的操作。

指令级是指基于某些指令能够单独进行。就相当于一个系统去同时处理多个不互相关联的信息。

数据级并行是基于同一指令集能同时对不同的数据集执行,是依赖于一个控制单元来指导不同的操作数集合上执行相同的操作。

任务级并行是基于不同的处理器能在相同或不同的数据集上执行不同的操作。就如同在流水线上分工各部分,下一个单位的输入是上一个的数输出。

共享内存并行处理器是让不同的处理器通过共享内存进行通信来解决各种计算形式的协调问题。

导图:

2019-2020-1学期 20202419《网络空间安全专业导论》第二周学习总结

原文:https://www.cnblogs.com/luoao/p/13855634.html