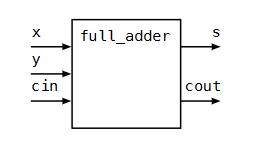

module full_adder(input x, input y, input cin, output s, output cout);

endmodule

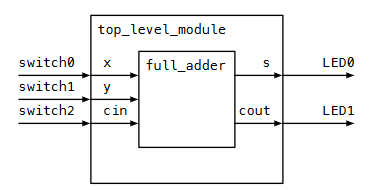

module top_level(input switch0,

input switch1,

input switch2,

output led0,

output led1

);

// instantiate the module full_adder, adder0 is his name

full_adder adder0(

.x(switch0),

.y(switch1),

.cin(switch2),

.s(led0),

.cout(led1)

);

endmodule

wire a;

wire b;

wire [7:0] c; // 8-bit wire declaration

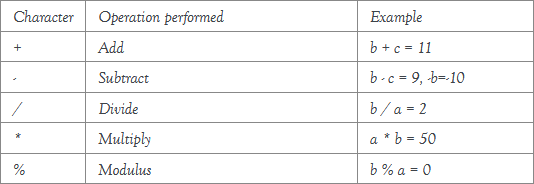

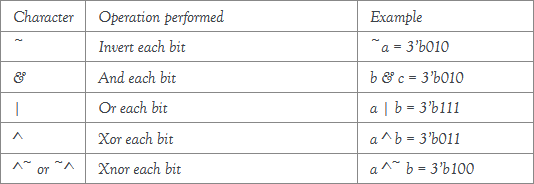

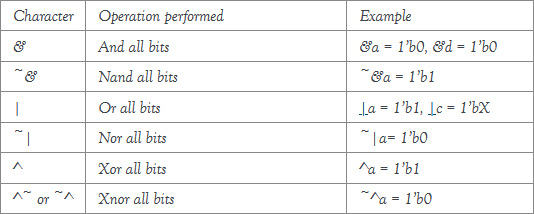

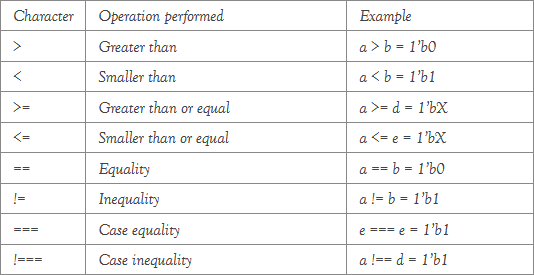

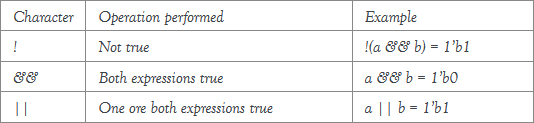

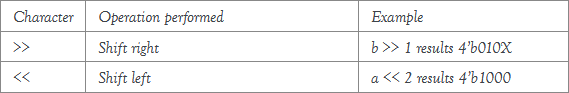

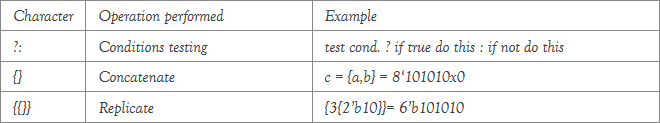

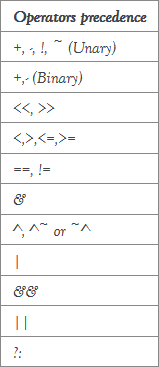

The order of the table tells what operation is made first, the first ones has the highest priority. The () can be used to override default.

// conditional operator ?:, this example is an expression that implements min(a, 10)

wire out;

assign out = a > 10 ? 10 : a;

// if a==b then c=0

// else if a<b then c=1

// else c=2

assign c = a==b ? 2‘d0 : (a<b ? 2‘d1 : 2‘d2);

`ifndef CONSTANTS // guard prevents header file from being included more than once, it is similar to the header file of C

`define CONSTANTS

`define ADDR_BITS 16

`define NUM_WORDS 32

`define LOG2(x) (x <= 2) ? 1 : \ // calculate the log2(x)

(x <= 4) ? 2 : (x <= 8) ? 3 : (x <= 16) ? 4 : (x <= 32) ? 5 : (x <= 64) ? 6 : -1

`endif

`include "constant.vh"

module memory (input [`ADDR_BITS - 1 : 0] address,

output [`LOG2(`NUM_WORDS) - 1 : 0] data

);

// implementation

endmodule

Verilog has two types of nets: wire and reg. Reg nets are required whenever a net must preserve state(i.e. in an always block). Wires are used for structural verilog(to connect inputs to outputs) and for continuous assignment.

verilog allows more complex logic through the use of always blocks.

Combinational logic(i.e. no state elements) can be written using always@(*). The value inside the parentheses is called the sensitivity list. Using a * will tell the compiler to compute the sensitivity list automatically(recommended for combinational logic)

Only reg nets can be assigned in an always block

input wire a;

input wire c;

output wire b;

reg b_out;

//

always @(*)

begin

b_out = ~a;

end

assign b = b_out;

// if-else statements

always @(*)

begin

if(a)

b_out = c;

else

b_out = ~c;

end

// case statement

always @(*)

begin

case(a)

0: b_out = c;

1: b_out = ~c;

default: b_out = c;

endcase

end

WARNING:

// This code will generate a latch

input [1:0] x;

reg [1:0] y;

always @(*) begin

if(x == 2‘b10)

y = 2‘d3;

else if(x == 2‘b11)

y = 2‘d2;

end

// y has a default value so that this code will not generate a latch

always @(*) begin

y = 2‘b00;

if(x == 2‘b10)

y = 2‘d3;

else if(x == 2‘b11)

y = 2‘d2;

end

Synchronous logic blocks are generated using special identifiers in the sensitivity list. Here we only want to update on the positive edge of the clock, so we use posedge. This will generate a synchronous circuit that implements x every clock cycle.

input clk;

reg [1:0] x;

always @(posedge clk)

begin

x <= x + 1;

end

Rules for picking a wire or reg net type:

1.localparam: Private module parameters are defined using the localparam directive. These are useful for constants that are needed only by a single local module, and it can not be instantiated with it

2.parameter: it‘s feature is similar to localparam, further more, it can transimit the parameter setting

For example, first define a module

module example #(parameter SIZE=7)

(input clk,

input rst_n,

output [SIZE-1 : 0] data

);

localparam K = 5;

reg [7:0] x;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

data <= 0;

else

data <= K + x;

end

endmodule

second when to instantiate the example module in the top level, and data size is required to modified as 32-bit

example EX1

#(.SIZE(32)) // 参数例化

(

.clk(clk),

.rst_n(rst_n),

.data(data)

);

-- wait to fill up

// A memory structure that has eight 32_bit elements

reg [31:0] fifo_ram [7:0];

fifo_ram[2] // represents the full 3rd 32-bit element

fifo_ram[5][7:0] // represents the lowest byte of 6th 32-bit element

`timescale 1ns/1ps

// a delay of #1 would result in a 1ns step

// Delays as low as #0.001 would be supported due to the resolution of 1ps

module tb;

reg clk_in;

reg rst_n;

wire clk_out;

reg a_in;

wire b_out;

initial

begin

clk_in = 0;

repeat (20) #10 clk_in = ~clk_in;

end

initial

begin

rst_n = 0;

#10;

rst_n = 1;

end

initial

begin

a_in = 0;

#10 a_in = 1;

#10 a_in = 0;

end

divider D1(

.clk_in(clk_in),

.clk_out(clk_out),

.rst_n(rst_n),

.a(a_in),

.b(b_out)

);

endmodule

原文:https://www.cnblogs.com/georgemxx/p/14002835.html