例子1:

(1)三相相位滞后,使用TBPHS寄存器

图59显示了一种利用模块间相位偏移的常见电源拓扑。该系统使用三个脉宽调制模块,模块1配置为主模块。要工作,相邻模块之间的相位关系必须是F = 120。这是通过将从TBPHS寄存器2和3分别设置为周期值的1/3和2/3来实现的。例如,如果周期寄存器加载了600个计数,则TBPHS(从机2) = 200,TBPHS(从机3) = 400。两个从模块都与主模块1同步。通过适当设置待定参数值,这一概念可以扩展到四个或更多阶段。下面的公式给出了N相的待定参数值:

例子:

TBPHS(N,M) = (TBPRD/N) x (—1)

Where:

N = number of phases

M = PWM module number

For example,

for the 3-phase case (N=3), TBPRD = 600,

TBPHS(3,2) = (600/3) x (2-1) = 200 (i.e., Phase value for Slave module 2)

TBPHS(3,3) = 400 (i.e., Phase value for Slave module 3)

/* * 日期:2018-1-27 * 功能:产生0度,120度,240度的PWM * 本例中,频率为1kHz,占空比为0.5,epwm1为主相位,2滞后120度,3滞后240度 * */

(2)EPWM配置

void InitEPwm1Example() { EPwm1Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm1Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 2 EPwm1Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm1Regs.AQCTLA.all = 0x0006; // ePWM1A 计数值等于0,置高电平;ePWM1A计数值等于PRD,置低电平。 EPwm1Regs.TBPRD = 37500; // 1KHz PWM 信号 EPwm1Regs.TBCTL.bit.SYNCOSEL = 1; // 当CTR = 0时,同步输出 } void InitEPwm2Example() { EPwm2Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm2Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 1 EPwm2Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm2Regs.AQCTLA.all = 0x0006; // ePWM2A 计数值等于0,置高电平;ePWM2A计数值等于PRD,置低电平。 EPwm2Regs.TBPRD = 37500; // 1KHz PWM 信号 EPwm2Regs.TBCTL.bit.PHSEN = 1; // 使能EPWM2相移 EPwm2Regs.TBCTL.bit.SYNCOSEL = 0; // 产生同步相位 EPwm2Regs.TBPHS.half.TBPHS = 12500; // 相移1/3,即120度 } void InitEPwm3Example() { EPwm3Regs.TBCTL.bit.CLKDIV = 0; // CLKDIV = 1 EPwm3Regs.TBCTL.bit.HSPCLKDIV = 1; // HSPCLKDIV = 1 EPwm3Regs.TBCTL.bit.CTRMODE = 2; // 增减计数模式 EPwm3Regs.AQCTLA.all = 0x0006; // ePWM3A 计数值等于0,置高电平;ePWM3A计数值等于PRD,置低电平。 EPwm3Regs.TBPRD = 37500; // 1KHz PWM 信号 EPwm3Regs.TBCTL.bit.PHSEN = 1; // 使能ePWM3相移 EPwm2Regs.TBCTL.bit.SYNCOSEL = 0; // 产生同步相位 EPwm3Regs.TBPHS.half.TBPHS = 25000; // 相移2/3,即240度 }

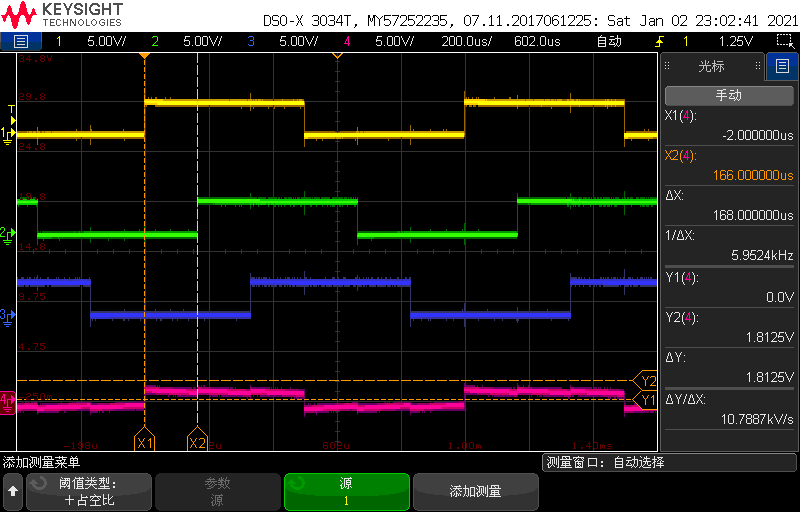

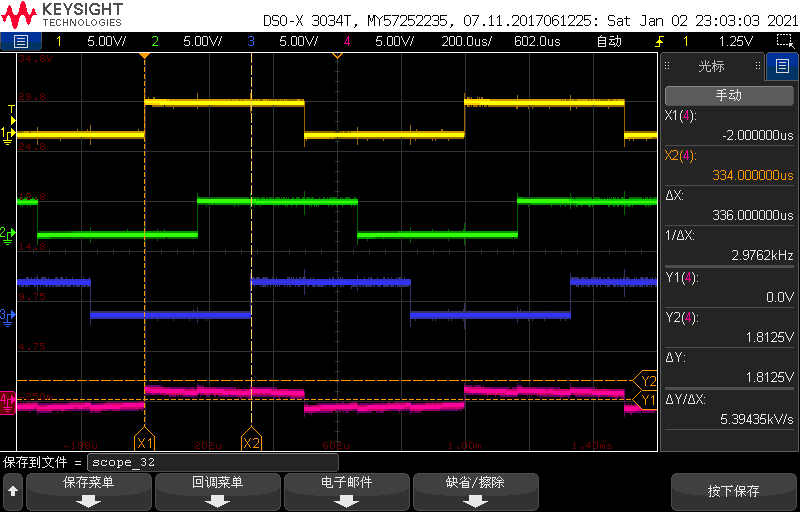

(3)生成的波形

1A超前2 1/3个周期,超前2/3个周期。

3.8 Controlling a 3-Phase Interleaved DC/DC Converter__控制三相交错DC/DC转换器

原文:https://www.cnblogs.com/stringer123456/p/14224497.html