连接实例

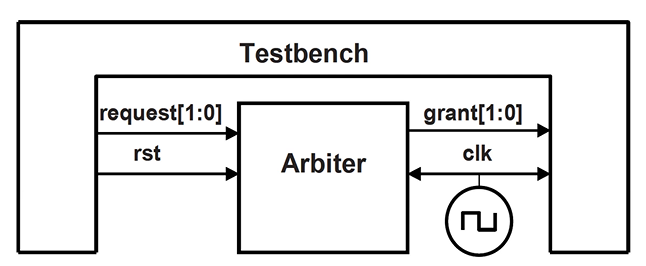

module top; wire [1:0] grant,request; wire clk, rest; arb a1(.grant(grant), .request(request), .reset(reset), .clk(clk)); test t1(.grant(grant), .request(request), .reset(reset), .clk(clk)); endmodule

// 方式1: module top; logic [1:0] grant,request; logic clk, rest; arb a1(.*); test t1(.*); endmodule // 方式2 module top; logic [1:0] grant,request; logic clk, rest; arb a1(.grant, .request, .reset, .clk); test t1(.grant, .request, .reset, .clk); endmodule

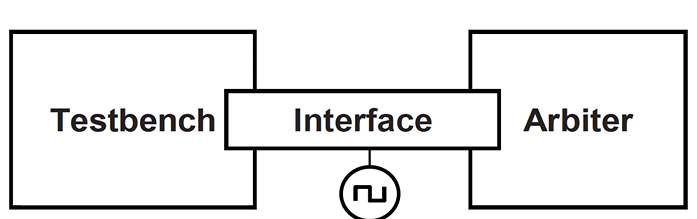

interface arb_intf(input bit clk); logic [1:0] grant, request; logic reset; endinterface

module test(arb_if arbif); initial begin @(posedge arbif.clk); arbif.request<=2‘b01; $display("@%0t:Drove req=01", $time); repeat(2) @(posedge arbif.clk); if(arbif.grant!=2‘b01) $display("@%0d:a1:grant != 2‘b01", $time); $finish; end endmodule

top.sV

module top; bit clk; always #5 clk=~clk; arb_if arbif(clk); // 方式1 arb a1 (arbif); test t1 (arbif); // 方式2 arb a1(.grant(arbif.grant), .request(arbif.request), .reset(arbif.reset), .clk(arbif.clk)); test t1(.grant(arbif.grant), .request(arbif.request), .reset(arbif.reset), .clk(arbif.clk)); endmodule

interface arb_intf(input bit clk); logic [1:0] grant, request; logic reset; modport TEST(outport request, reset, input grant, clk ); modport DUT(input request, reset,clk, output grant); endinterface module arb(arb_intf.DUT arbif); ... endmodule module test(arb_intf.TEST arbif); ... endmodule

在驱动时,添加响应的认为延迟;模拟真实的延迟行为,同时加大clk与变量之间的延迟,以提高DUT使用信号时的准确度和TB采样信号时的可靠性

clocking bus @(posedge clock1); // 定义时钟上升沿驱动和采样 default input #10ns output #2ns; // 上升沿的前10ns对其进行输入采样,事件后的2ns对其进行输出驱动 input data, ready, enable; // 声明要采样的三个输入信号,采样事件使用默认输入事件,上升沿的前10ns output negedge ack; // 声明要驱动的ack信号,驱动事件为下降沿,覆盖了原来的默认输出事件,上升沿后的2ns input #1step addr; // 自定义的采样事件,上升沿前的1step,这个1step使采样发生在上升沿的上一个时间片采样区域,即可采样到的数据是上一个时钟周期的数据 endcloking

原文:https://www.cnblogs.com/gareth-yu/p/14261771.html