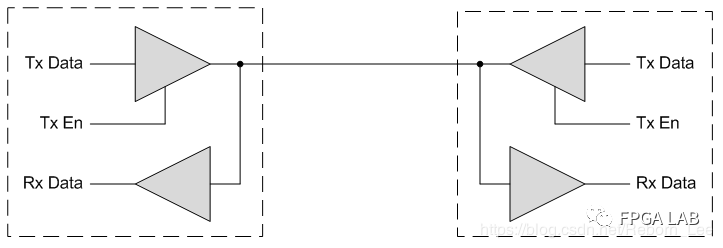

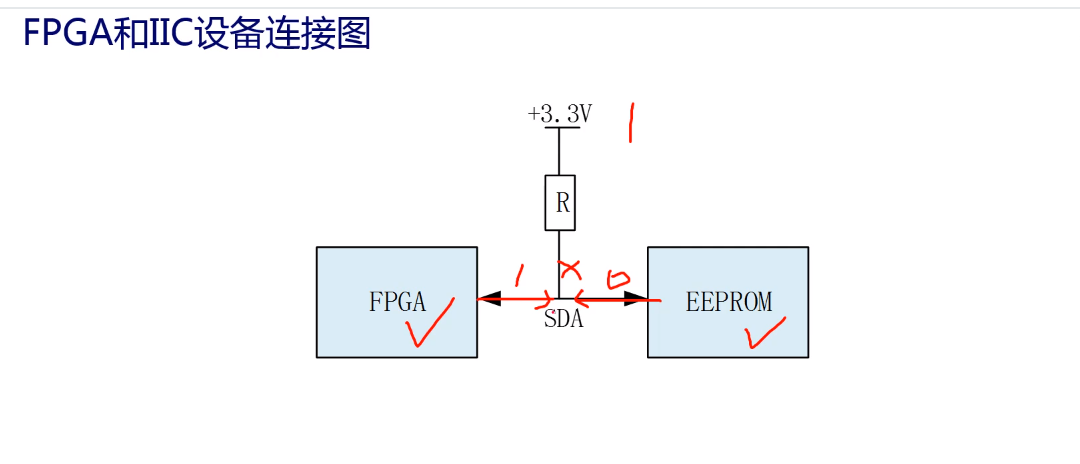

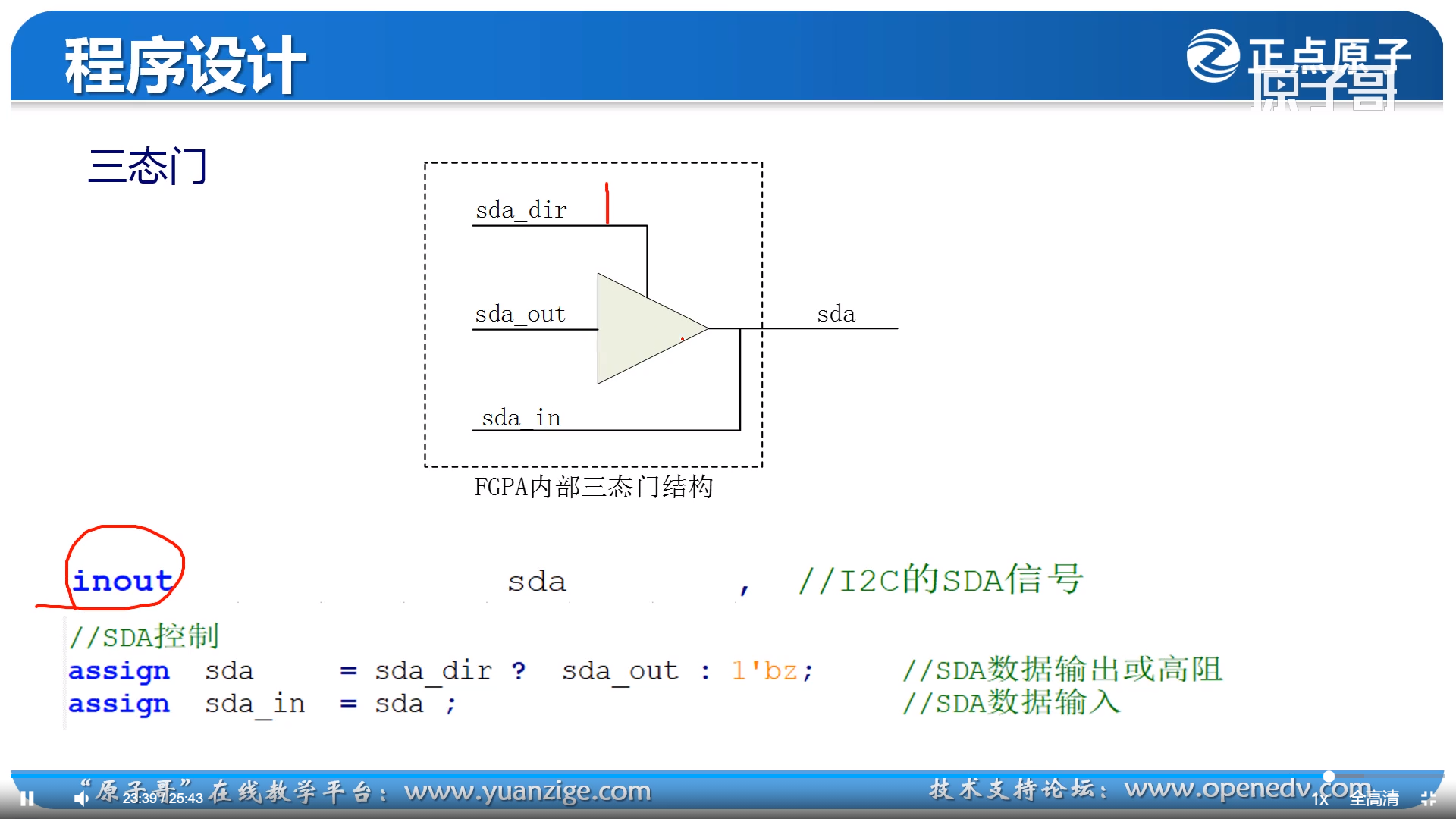

信息双向传输的时候需要。 也就是引脚定义为inout的时候。

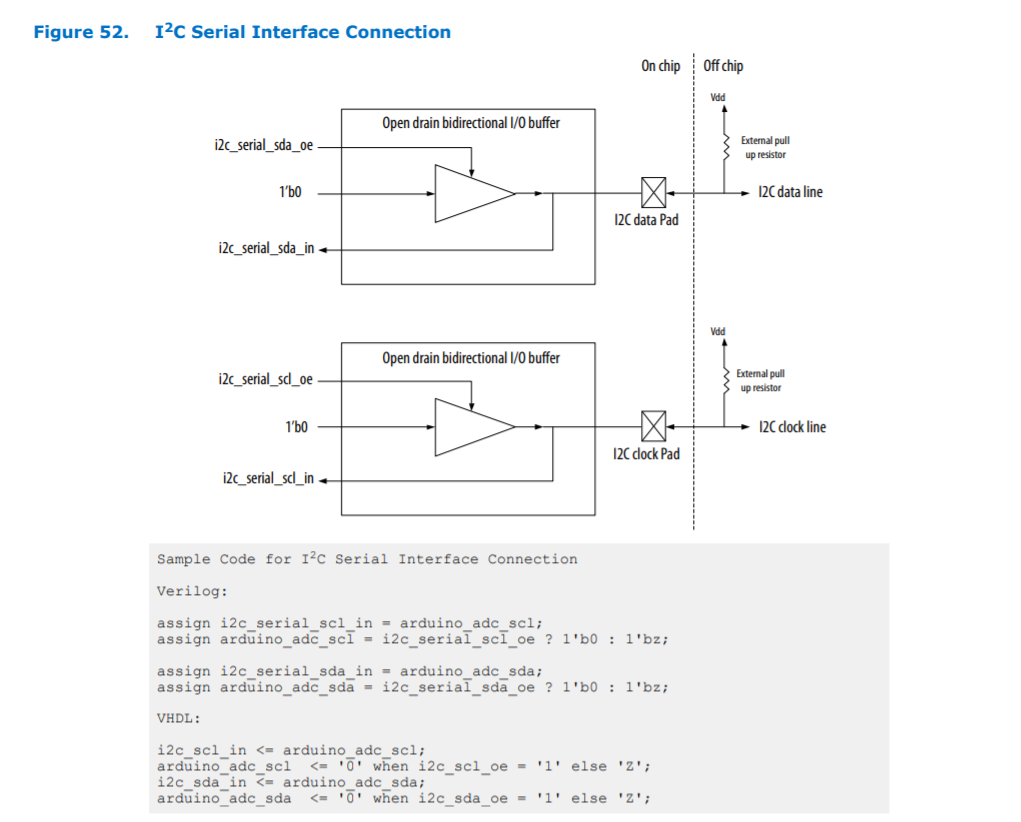

Intel 的 IP 文档:

https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ug/ug_embedded_ip.pdf

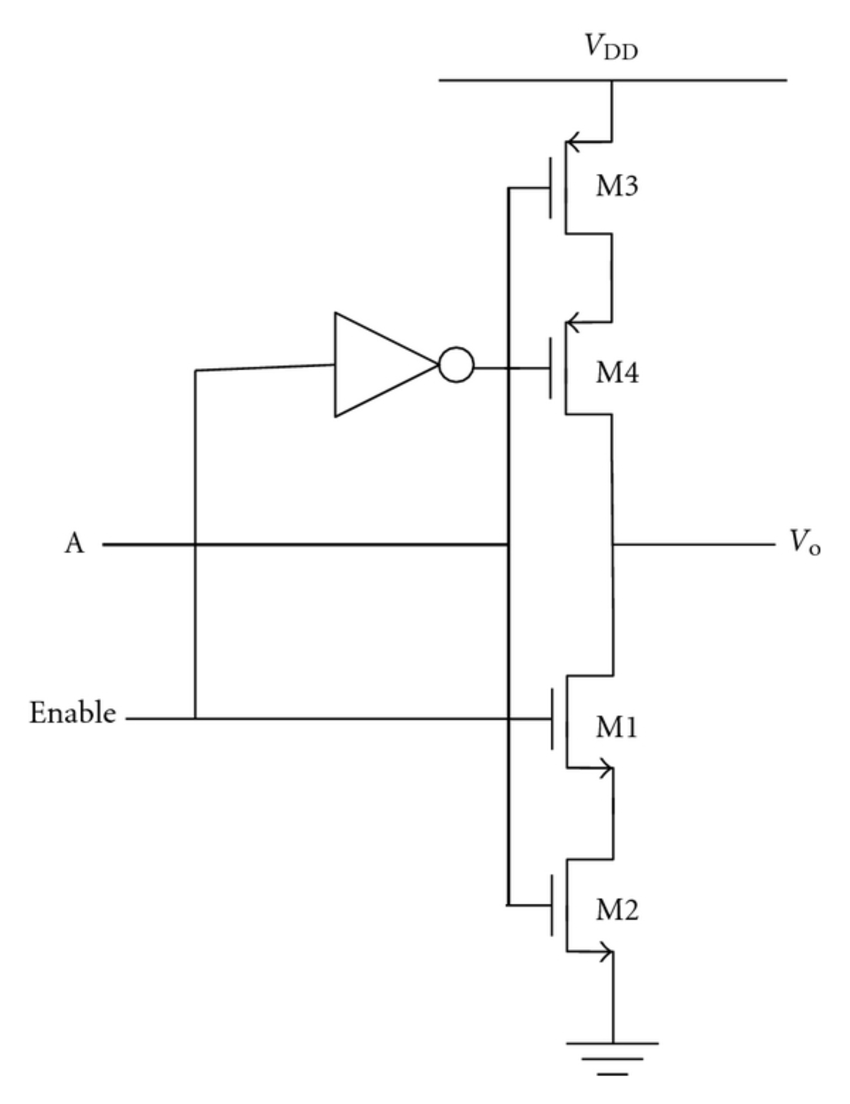

dir 是1时, out = sda,dir 是 0 时,三态门输出高阻, 也就是电阻无限大 相当于断开, 然后 外部加上拉电阻,于是输出是1。

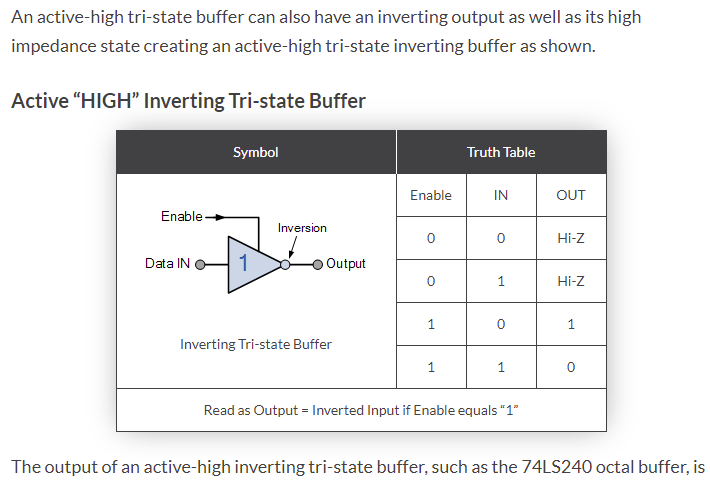

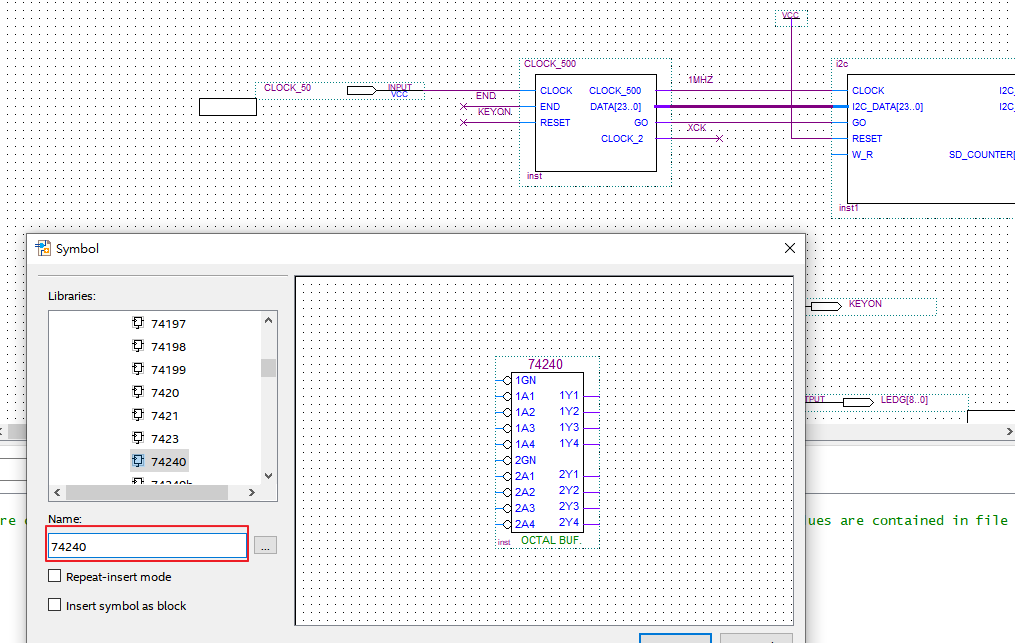

最近有学生问tri-state buffer / Inverter(如下图)怎么实现?有两种办法:

原文:https://www.cnblogs.com/DoreenLiu/p/14637800.html