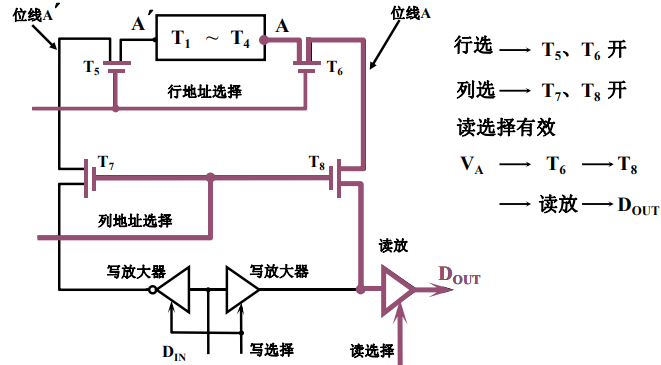

当T6,T8打开后,A端信号通过T6,T8传输到读选择三态门实现输出

同时,对A‘信号而言,T5,T7开关也打开 ,但是由于到写放大器处无法传输通过,因此无法传输

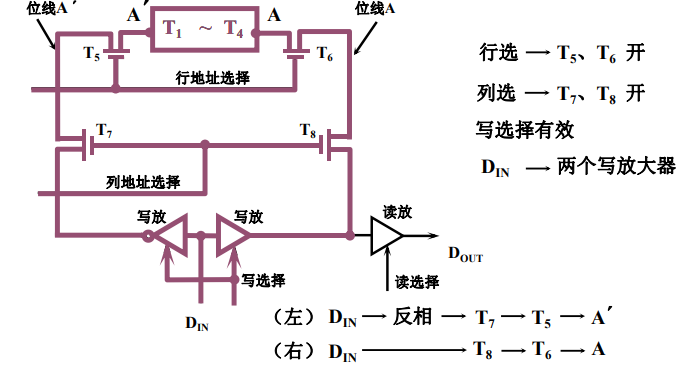

数据从Din 输入,经过两个三态门,向A‘和A中分别写入相反的数据

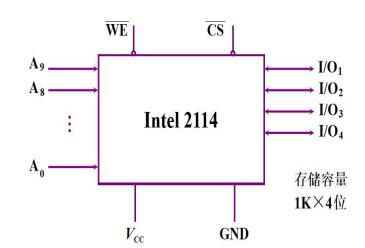

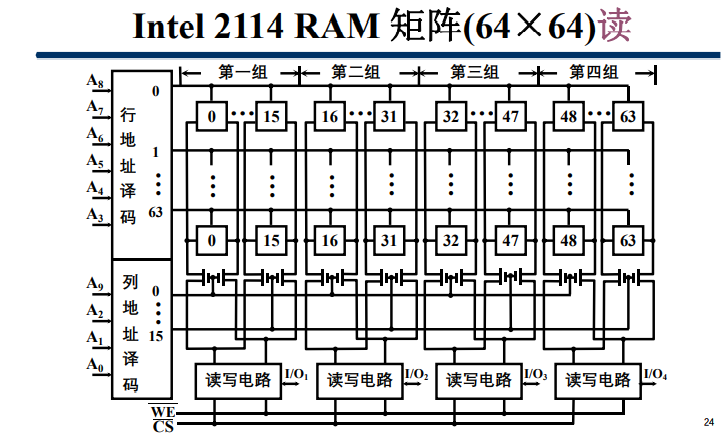

静态RAM芯片举例:Intel 2114

IO接口为4位,则每一次需要进行4位的读写操作

对于行地址译码器而言,其共有64根导线,每一次译码后只激活一根导线,

对于列地址译码器而言,其共有16根导线,每一次译码后,需要激活4根导线

因此,将64*64矩阵,在列方向上分为4组,每一次译码后,激活每一组的对应导线

例如,行地址译码为0,则第0行所有存储单元被选中,列地址译码为0,则每一组第0列所有单元被选中,共4位,然后根据WE和CS信号,完成读写操作

原文:https://www.cnblogs.com/SValley/p/14672040.html