例:给出一CPU,地址线16根,数据线8根,MREQ访存控制信号(低电平有效),WR 读/写控制信号(高电平为读,低电平为写)

给出RAM1K*4位, 4K*8位, 8K*8位,

给出ROM2K*8位, 4K*8位, 8K*8位。

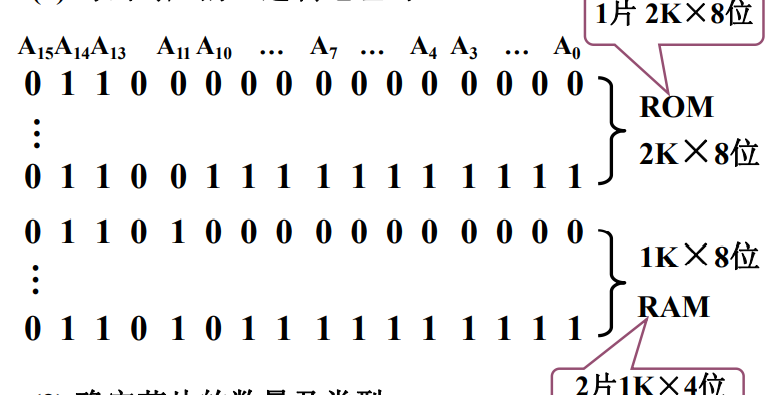

要求6000H~67FFH 为系统程序区; 6800H~6BFFH 为用户程序区。完成CPU和存储器连接。

步骤:

其它地址线作为片选信号

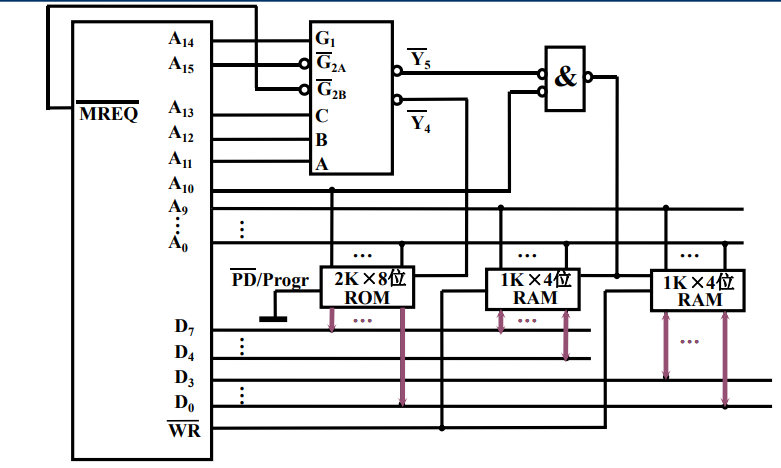

这里使用74LS138译码器,A11, A12,A13作为信号接入,需要注意的是,MREQ信号必须在片选信号中体现,该信号的作用是确定该地址访问的是存储器而不是IO接口,如果没有这个信号,那对IO接口的访问的同时也会访问存储器,导致数据冲突。

LS138译码器的输出端,当输出Y4的时候(对应输入为100),选中的是ROM,当输出Y5(对应101)的时候,选中的是ROM。这里需要注意的是,选中RAM要求Y5和A10作与运算,这是因为对RAM而言,不仅要138译码器输出的是Y5,同时也得要求A10为0,这样才能读取RAM(或者说当A10为1的时候,这时对应的是别的存储芯片);而对ROM而言,其地址线包含A10,即不论A10是0还是1,都能够选中芯片内相应的地址。

原文:https://www.cnblogs.com/SValley/p/14689309.html