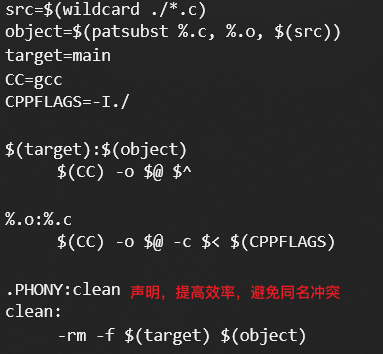

Makefile 就像是一个Shell脚本一样,通过批量处理,来完成自动化编译

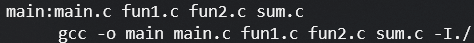

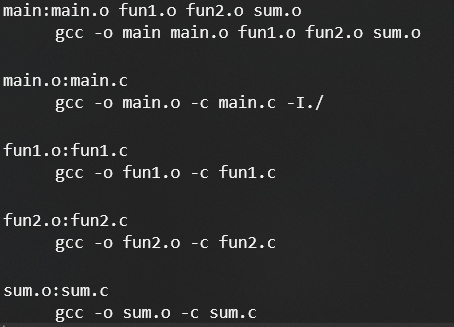

目标:依赖

(tab缩进)命令

修改一个文件,所有的文件都需要重新编译

但是此方法当依赖较多时比较麻烦

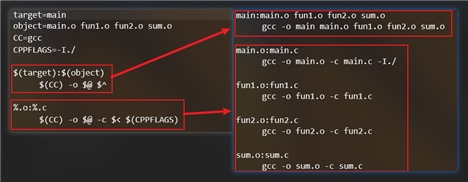

直接使用=进行赋值,使用$(变量名)引用

var=abc

var2=$(var)

CC = gcc #arm-linux-gcc

CPPFLAGS : C预处理的选项 -I

CFLAGS: C编译器的选项 -Wall -g -c

LDFLAGS : 链接器选项 -L -l

$@ 表示规则中的目标

$< 表示规则中的第一个条件

$^ 表示规则中所有条件

同时可以使用%作为通配符直接代表目标名和依赖名,但需注意,%代表一个或多个同时目标和依赖名必须一致

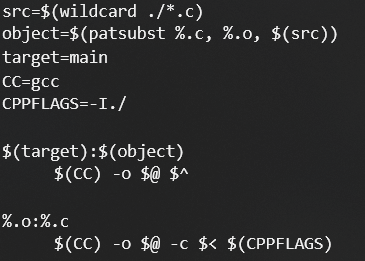

常用的两个

1. wildcard – 查找指定目录下的指定类型的文件

src=$(wildcard *.c) //找到当前目录下所有后缀为.c的文件,赋值给src

2. patsubst – 匹配替换

obj=$(patsubst %.c,%.o, $(src)) //把src变量里所有后缀为.c的文件替换成.o

当程序编译完成后,文件夹中还存在很多编译过程中生成的预编译文件,最后一步就是清理这些文件

原文:https://www.cnblogs.com/cokefentas/p/14802242.html