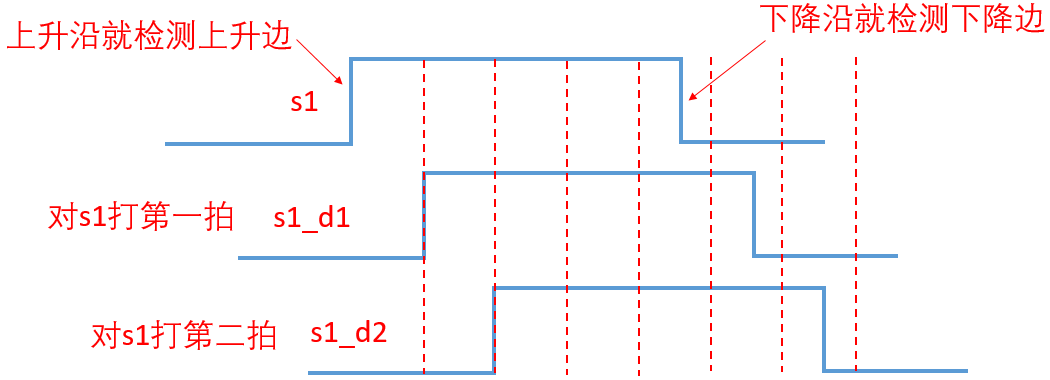

在需要基于一个外部输入信号的操作中,又特别是此输入信号可能输出亚稳态的情况,此时对输入信号打两拍和边沿检测,是个不错的方法,如下

打两拍+边沿检测代码

1 //对S1输入信号打第一拍 2 always @(posedge clk or negedge rst_n) 3 if(!rst_n) 4 s1_d1 <= 1‘b0; 5 else 6 s1_d1 <= s1; 7 8 //对S1输入信号打第二拍 9 always @(posedge clk or negedge rst_n) 10 if(!rst_n) 11 s1_d2 <= 1‘b0; 12 else 13 s1_d2 <= s1_d1; 14 15 //上升沿检测,pedge为高,则表示检测到上升沿 16 assign pedge= (s1_d1 && (~s1_d2)); 17 18 //下降沿检测,nedge为高,则表示检测到下降沿 19 assign nedge= ((~s1_d1) && s1_d2);

原文:https://www.cnblogs.com/QSHL/p/14825228.html