通常在执行 make 时,如果通过命令行定义了一个变量,那么它将替代在 Makefile中出现的同名变量的定义。

就是说,对于一个在 Makefile 中使用常规方式(使用“=”、“:=”或者“define”)定义的变量,我们可以在执行 make 时通过命令行方式重新指定这个变量的值,命令行指定的值将替代出现在 Makefile 中此变量的值。

如果不希望命令行指定的变量值替代在 Makefile 中的变量定义,那么我们需要在 Makefile 中使用指示符“override”来对这个变量进行声明。

实际情况下,我们经常会有这种需求:通过命令行指定一些附加的参数选项,对于一些通用的参数选项在makefile中指定.

make命令行指定的变量值将会覆盖makefile中定义的同名的变量值

SRCS := A.c B.c C.c all: @echo "SRCS: " $(SRCS)

make命令行指定的变量值将不会覆盖makefile中定义的同名的变量值,所以override有保护makefile中变量值不被命令行参数修改的作用。

override SRCS := A.c B.c C.c all: @echo "SRCS: " $(SRCS)

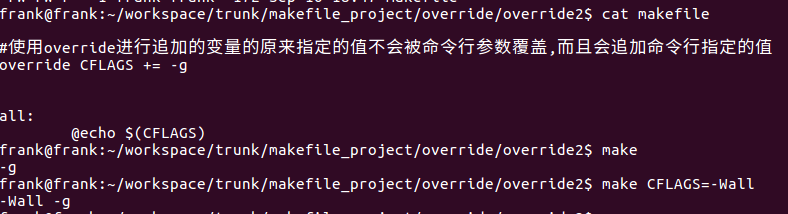

#使用override,对于进行追加的变量,原来指定的值不会被命令行参数覆盖,而且会追加命令行指定的值 override CFLAGS += -g all: @echo $(CFLAGS)

原文:https://www.cnblogs.com/god-of-death/p/14842204.html