本设计预实现720P到1080P的图像放大,输入是YUV444数据,分量像素位宽为10bit,采用的算法为双线性插值法,开发平台是xiinx K7开发板。

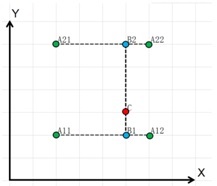

双线性插值法即双次线性插值,首先在横向线性插值,然后在纵向线性插值,如图1所示。

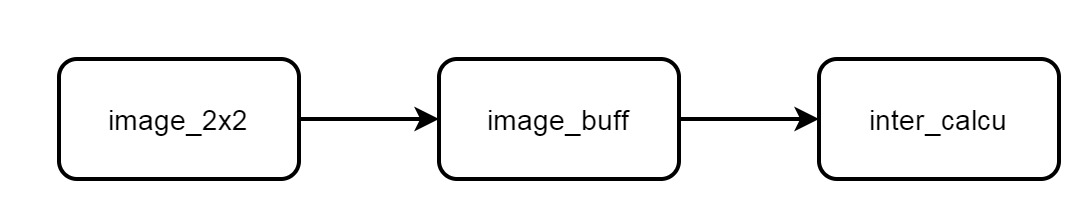

图1 双线性插值原理 图2 双线性插值FPGA结构

在FPGA中实现主要依靠双线性插值计算公式,即:

P_new=(1-dx)(1-dy)P1+dx(1-dy)P2+(1-dx)dyP3+dxdyP4

为减少乘法的使用,转换为

P_new=P1+[(P4-P3)+(P1-P2)]dxdy-(P1-P2)dx+(P3-P1)dy

其中,P1,P2,P3,P4指的是待插值点周围4个像素点。根据公式可以将插值计算分为3部分:1.相邻像素点(2x2像素模板)的求取。

2.插值系数的求取以及插值系数的计算。同时为达到流水线处理,在获取2x2像素模板后加一级缓存,所以最终的FPGA实现结构如图2所示。其中,

本次设计是对YUV3个分量分别作插值处理,所以使用了3个双线性插值模块。

image_2x2模块用于求取像素点2x2模板,使用2级双口bram级联实现(如果分辨率低可选择移位寄存器)。每个bram缓存一行图像数据,并

在bram输出端插入寄存器作同步用,按照2x2模板位置取出数据,并拼接成40bit。注意:当像素点在边缘时,则采取像素复制的方式得到2x2模板,

即有效像素点取不到的位置使用相邻点替代。

image_buff模块用于2x2像素模板的缓存,输入为40bit(4个像素点),使用两个bram乒乓操作实现。该模块的读地址拉出,供inter_calcu模块

读取像素点数据。

inter_calcu模块用于插值系数的求取和插值系数的计算,是双线性插值算法的核心模块。该模块主要通过缩放坐标转换公式反推原始坐标,然后

根据原始坐标取出前一级image_buff模块数据。转换公式为:

srcx=(dstx+0.5)*(src_width/dst_width)-0.5,即dstx=(srcx+0.5)*(dst_width/src_width)-0.5,Y方向同理。

当前像素点一直流转,即可反推出原始坐标,同时由于FPGA不善于处理浮点数,将其定点化,左移。在本此设计中,src_width/dst_width = 1280/1920 = 2/3,

最后有公式:

128srcx = 85.33dstx-21.33,即 2^13*srcx = {7‘d85,6‘b010101}dstx-{7‘d21,6‘b010101};

根据该公式可推算出sryx,srcy的值,其整数为2x2模板的bram坐标({srxy,srcx}),其小数部分即为双线性插值计算公式中的dx,dy。反推坐标部分代码如下所示:

//Intermediate coefficient,插值坐标计算

//反推坐标

assign P1=bram_rddata_i[39:30];

assign P2=bram_rddata_i[29:20];

assign P3=bram_rddata_i[19:10];

assign P4=bram_rddata_i[9:0];

assign corx_wire=(dstx==11‘d0)?{7‘b0010101,6‘b010101}:{7‘b1010101,6‘b010101}*dstx-{7‘b0010101,6‘b010101};

assign srcx=corx_wire[23:13];

assign dx=corx_wire[12:0];

assign cory_wire=(dsty==11‘d0)?{7‘b0010101,6‘b010101}:{7‘b1010101,6‘b010101}*dsty-{7‘b0010101,6‘b010101};

assign srcy=cory_wire[23:13];

assign dy=cory_wire[12:0];

至此,双线性插值公式中的dx,dy,P1,P2,P3,P4便全部求出,即可计算双线性插值。为达到更好的时序,最后选用4级流水线的方式实现该公式:

P_new=P1+[(P4-P3)+(P1-P2)]dxdy-(P1-P2)dx+(P3-P1)dy,即[(P4-P3)+(P1-P2)]为一级,[(P4-P3)+(P1-P2)]dx为一级,[(P4-P3)+(P1-P2)]dxdy为第三级,

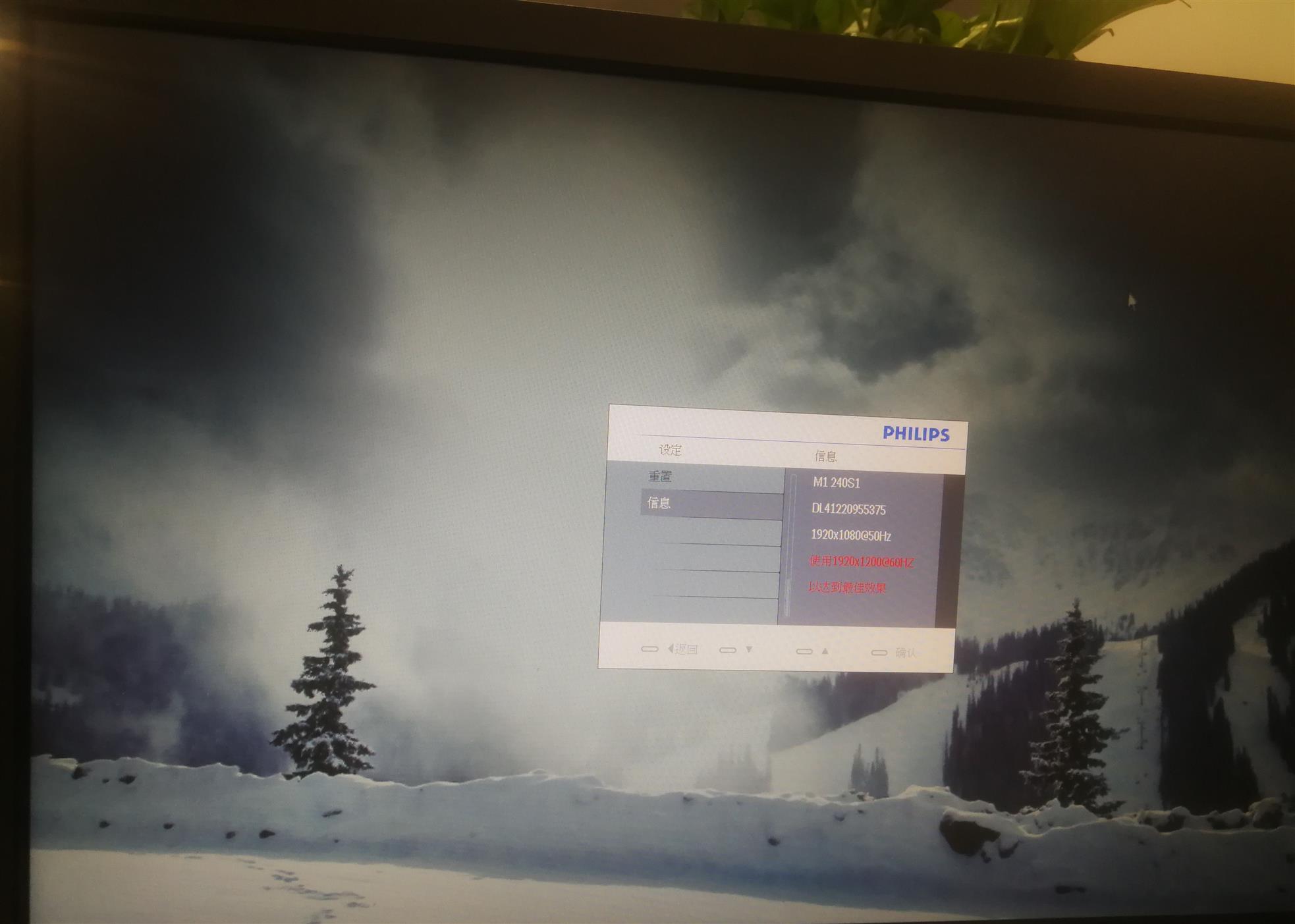

总的加法为第四级,最后实现的效果如图3和图4所示。

图3 720P SDI视频源

图4 缩放后效果图

原文:https://www.cnblogs.com/peiyu758/p/14883707.html