可以做为参考---->> https://www.zhihu.com/column/c_1131528588117385216

the compiler knows where to find the module

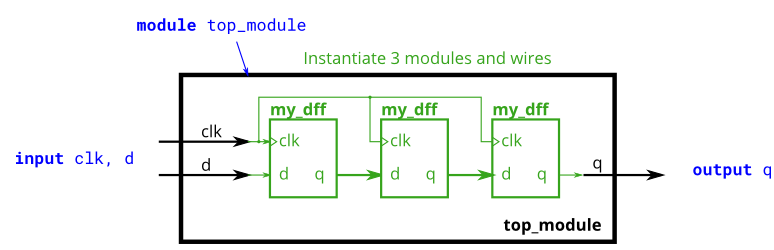

Module shift

module top_module ( input clk, input d, output q ); //内部是三个相同的module,内部是输入传到输出,这个昨弄?? wire q1,q2,q3; //缓存一下中间的信号 my_dff dff1(.clk(clk),.d(d),.q(q1)); my_dff dff2(.clk(clk),.d(q1),.q(q2)); my_dff dff3(.clk(clk),.d(q2),.q(q3)); assign q=q3; //吼吼吼,成功了 endmodule

module full_adder4( input [3:0] a , //adder1 input [3:0] b , //adder2 input c , //input carry bit output [3:0] so , //adding result output co //output carry bit ); wire [3:0] co_temp ; //第一个例化模块一般格式有所差异,需要单独例化 full_adder1 u_adder0( .Ai (a[0]), .Bi (b[0]), .Ci (c==1‘b1 ? 1‘b1 : 1‘b0), .So (so[0]), .Co (co_temp[0])); genvar i ; generate for(i=1; i<=3; i=i+1) begin: adder_gen full_adder1 u_adder( .Ai (a[i]), .Bi (b[i]), .Ci (co_temp[i-1]), //上一个全加器的溢位是下一个的进位 .So (so[i]), .Co (co_temp[i])); end endgenerate assign co = co_temp[3] ; endmodule

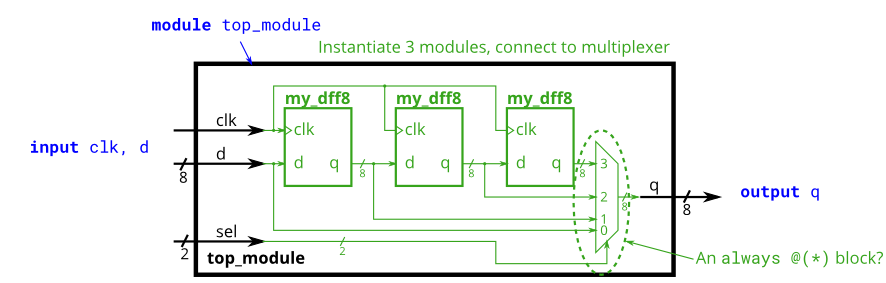

module top_module ( input clk, input [7:0] d, input [1:0] sel, output [7:0] q ); //wire [7,0] tmp1,tmp2,tmp3;//傻了,这vector中间是冒号是冒号是冒号是冒号! wire [7:0] tmp1,tmp2,tmp3; my_dff8 m1(clk,d,tmp1); my_dff8 m2(clk,tmp1,tmp2); my_dff8 m3(clk,tmp2,tmp3); always @(*) case (sel) //2‘b00:q=d; //2‘b01:q=tmp1; //2‘b02:q=tmp2; //2‘b03:q=tmp3; //这都是啥,太低级的错误了,看来需要休息一下了 2‘d00:q=d; 2‘d01:q=tmp1; 2‘d02:q=tmp2; 2‘d03:q=tmp3; endcase endmodule

-----------有点不太清醒了,明天再看看----------20210729-------------------

原文:https://www.cnblogs.com/czShare/p/15077482.html